# ECE290 Fall 2012 Lecture 20

Dr. Zbigniew Kalbarczyk

# Today

- Central Processing Unit

- LC-3 Architecture

- A program example

- Assembly instructions

- Binary instructions

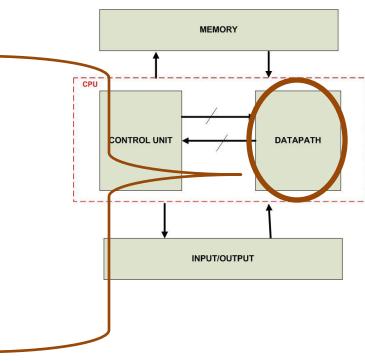

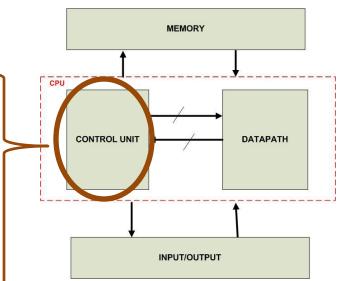

## **Components of a Simple Computer**

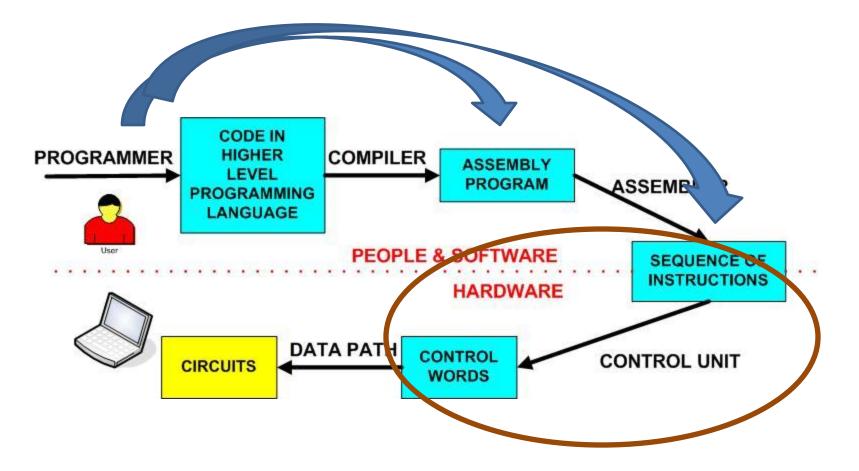

Before: Focus on MEMORY designing a control unit of a CPU in a CPU simple computer *Now:* Focus on CONTROL UNIT DATAPATH understanding a control unit of a CPU in a sophisticated <u>computer</u> INPUT/OUTPUT

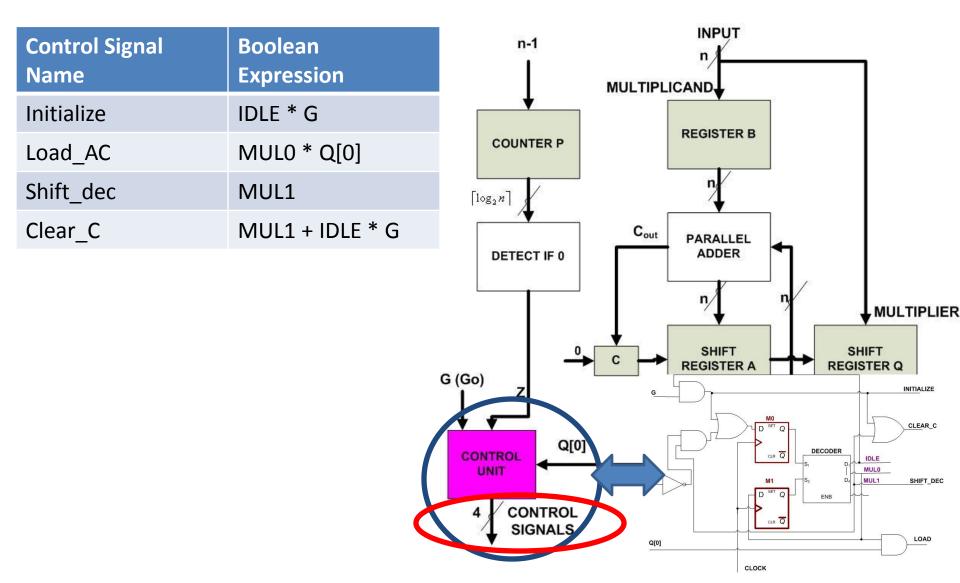

#### **Before:** Binary Multiplier: Data Path & Control Unit

### Now: Little Computer (LC) - 3

- The LC-3 serves as a transition from a single purpose (binary multiplier) to a multi-purpose real CPU

- The LC-3 has all the important characteristics of microprocessors

- The Intel 8080 (in the first IBM PC ~ 1981)

- The Motorola 68000 (in the Macintosh ~ 1984)

- The Pentium IV (in PCs ~ 2003)

- .....

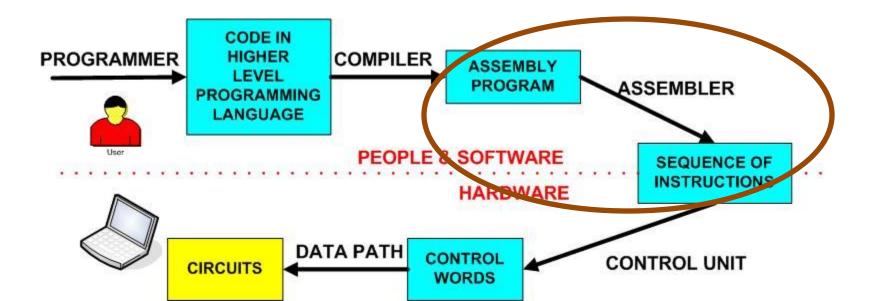

#### **Interfacing LC-3**

We study the process of translating a sequence of instructions to control words

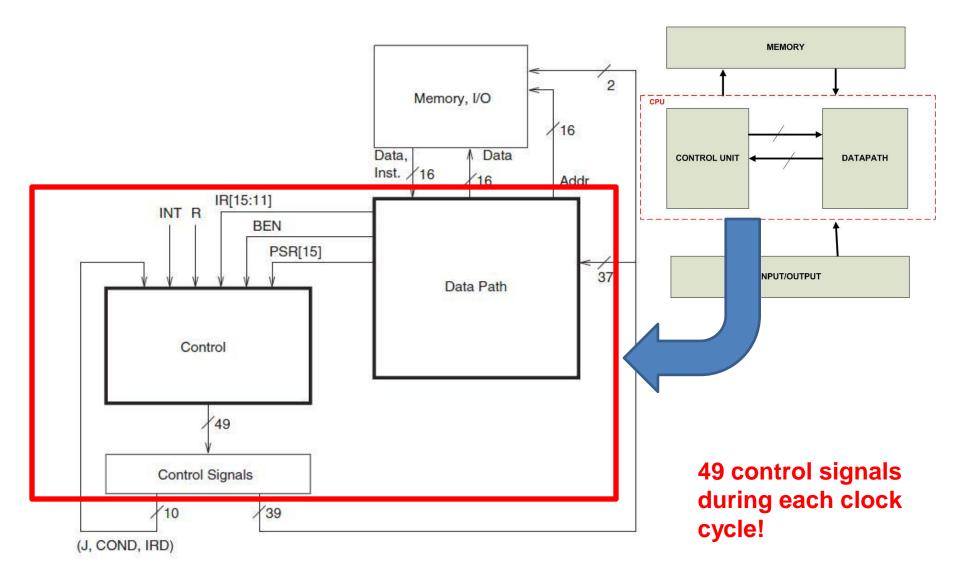

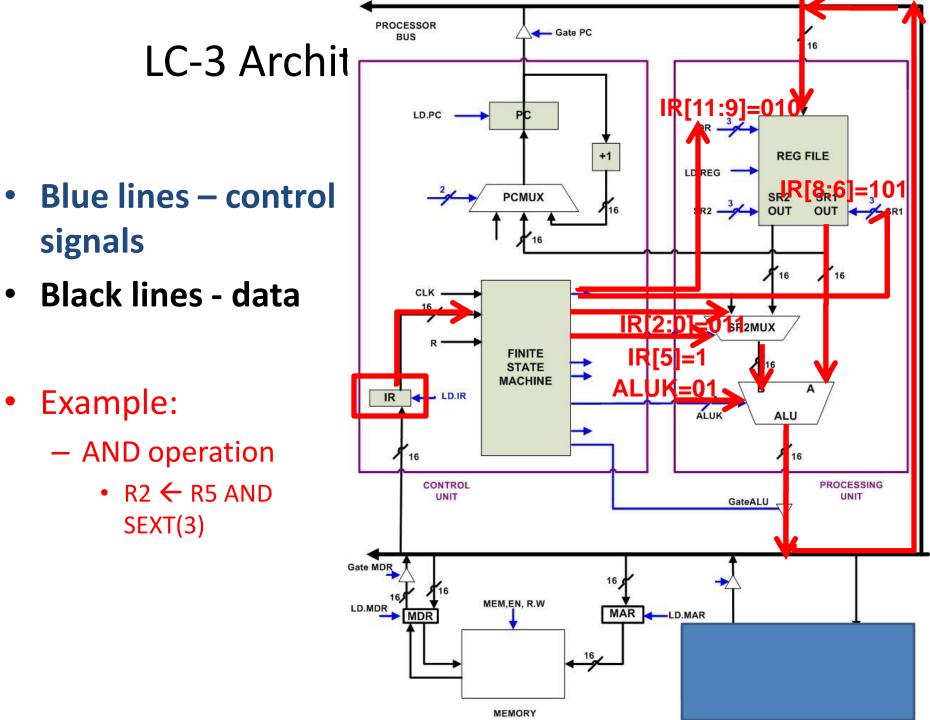

#### LC-3: Major Components

#### Signals from Data Path to Control

- IR[15:11] are the opcode bits

- PSR[15] is the bit [15] of the Processor Status Register, which indicates whether the current program is executing with supervisor or user privileges.

- **BEN** is to indicate whether or not a BR (conditional branch) should be taken.

- INT is to indicate that some external device of higher priority than the executing process requests service.

- **R** is to indicate the end of a memory operation.

## LC-3: Memory Description

- Memory Unit:

- $2^{16} \times 16 \text{ RAM}$  (64K x 2Bytes = 128KB)

- Memory Address Register (MAR): 16 bits (64K)

- Memory Data Register (MDR): 16 bits (one word)

- Memory Units in Existing Processors

- Intel's PENTIUM IV ~ MDR= 32 bits

- Sun's Sparc-V9 & Intel's Itanium ~ MDR= 64 bits

- Pagers, VCRs, cell phones ~ MDR = 8bits

## LC-3: CPU Description

- CPU:

- Data Path: Register File

- General purpose registers R0-R7

- Each register has 16 bits

- Data Path: ALU

- One arithmetic operation (ADD)

- Two logical operations (bitwise AND and bitwise complement)

- Compare with Sun's Sparc-V9

- 32 registers (64 bits ~ word)

## LC-3: CPU Description

#### • CPU

#### – Control Unit:

- Program Counter (PC) 16 bit address of next instruction

- Instruction register (IR) 16 bit word from memory interpreted as instruction

- Condition codes NZP each N or Z or P indicates whether the result was negative (100), zero (010) or positive (001)

**Note**: Some registers (e.g., PC, MAR) are not directly addressable by the end user but are used by instructions

## LC-3: Instruction Set Architecture (ISA)

- LC-3 ISA is the complete specification of the interface between programs and the underlying computer architecture

- ISA is the information required to write machine language program

#### LC-3 ISA: Instruction Set

- Instruction Set:

- a set of instructions the LC-3 can execute

- Instruction Format:

- binary representation of instructions (2 bytes ~ word)

- Instruction List: (There are 16 opcodes)

- Operations

- Operate: ADD, AND, NOT

- Data movement: LD, LDI, LDR, LEA, ST, STI, STR

- Control: BR, JMP, JSR, JSRR, RET, RTI, TRAP

- Data types: 16 bit 2's complement numbers

#### LC-3 ISA: Addressing Modes

- Where are the operands?

- register, memory, immediate

- How is location of an operand specified?

- Non-memory addresses

- Register,

- Immediate (literal)

- Memory addresses

- Program counter relative,

- Base + offset,

- Indirect

LC-3 ISA: Li AND<sup>+</sup>

- **Operations** AND<sup>+</sup>

- Operate: ABR

- Data move<sup>JMP</sup>

– **Control:** BI<sup>JSR</sup>

JSRR

$LDI^+$

#### $LD^+$

#### **Notation:**

DR .. Destination regis LDR<sup>+</sup> SR ....Source register (LEA<sup>+</sup> Imm5 ... A 5 bit immed NOT<sup>+</sup> BaseR ... R0-R7 offset6 ... BaseR + off:RET PCoffset9 ... PC+[-256 ST PCoffset11...PC+[-102 SEXT(A) ... sign-exten(STI ZEXT(A) ... zero-exten(STR) Setcc() ... indicates the

| 15 14 13 12 |     |     |          |     |       | 5     |       |       | 2 1 | 0 |

|-------------|-----|-----|----------|-----|-------|-------|-------|-------|-----|---|

| 0001        |     | DR  |          | SF  | 11    | 0     |       | )     | SR2 | 2 |

| 0001        |     |     |          | SF  | 71    | 1     |       | im    | im5 |   |

| 0101        |     | DR  |          | SF  | 71    | 0     |       |       | SR2 | 2 |

| 0101        |     | DR  |          | SF  |       | 1     | 2.2   | im    | im5 |   |

| 0000        |     | z   |          |     | 1     |       | offse | et9   |     |   |

| 1100        |     | 000 |          | Bas | eR    | ~~~   | (     | 0000  |     |   |

| 0100        | 1   |     | ı<br>ı   |     | PC    | offse | et11  |       |     |   |

| 0100        | 225 | 0   | <u> </u> |     | еR    | 33    | (     | 0000  |     |   |

| 0010        |     |     |          |     |       | PC    | offse | et9   |     |   |

| 1010        |     |     |          | 3   | 1     | PC    | offse | et9   |     |   |

| 0110        |     |     |          | Bas | ieR   |       |       | offse |     |   |

| 1110        |     |     |          |     | a - 1 | PC    | offse | et9   |     |   |

| 1001        |     | DR  |          | s   | R     |       |       |       |     |   |

| 1100        |     | 000 |          | 11  | 1     |       | (     | 0000  |     |   |

| 0011        |     | SR  |          |     |       |       | offse |       |     |   |

| 1011        |     | SR  | 1        |     | i i   | PC    | offse | et9   |     |   |

| 0111        |     | SR  |          | Bas |       |       |       | offse |     |   |

superscript "+" denotes instructions that update the condition bits NZP

| DR ← SR1 + SR2;<br>set NZP                                                              |

|-----------------------------------------------------------------------------------------|

| $DR \leftarrow SR1 + SEXT(imm5);$<br>set NZP                                            |

| DR ← SR1 AND SR2;<br>set NZP                                                            |

| $DR \leftarrow SR1 AND SEXT(imm5);$<br>set NZP                                          |

| IF $((n \cdot N)+(z \cdot Z)+(p \cdot P))$<br>THEN PC $\leftarrow$ PC + SEXT(PCoffset9) |

| $PC \leftarrow BaseR$                                                                   |

| R7 ← PC<br>PC ← PC + SEXT(PCoffset11)                                                   |

| $R7 \leftarrow PC$<br>PC $\leftarrow$ BaseR                                             |

| $ \begin{array}{l} DR \leftarrow M[PC + SEXT(PCoffset9)]; \\ Set \ NZP \end{array} $    |

| DR ← M[M[PC + SEXT(PCoffset9)]];<br>Set NZP                                             |

| $DR \leftarrow M[BaseR + SEXT(offset6)];$<br>Set NZP                                    |

| $DR \leftarrow PC + SEXT(PCoffset9);$<br>Set NZP                                        |

| DR ← NOT(SR);<br>Set NZP                                                                |

| $PC \leftarrow R7$                                                                      |

| $M[PC + SEXT(PCoffset9)] \gets SR$                                                      |

| $M[M[PC + SEXT(PCoffset9)]] \leftarrow SR$                                              |

| $M[BaseR + SEXT(offset6)] \gets SR$                                                     |

#### LC-3: Using Operate Instructions

- How do we execute other operations than ADD, AND and NOT?

- **Copy:** R1 ← R2

- − Strategy: R1 ← R2 + 0 (immediate)

- **Clear:** R1 ← 0

- − Strategy: R1 ← R1 AND 0 (immediate)

- **Subtract:** R1 ← R2 − R3

- − Strategy 1: R1 ← NOT R3; R1 ← R1 +1; R1 ← R2 + R1

- R1 <- R2 and 2's complement of R3

- Strategy 2: if 2<sup>nd</sup> operand VAL is small then R1 ← R2 + VAL (immediate)

#### LC-3: Using Operate Instructions

- OR: R1 ← R2 OR R3

- Strategy:

| <b>Register Operation</b> | <b>Boolean Operation</b>                     |  |

|---------------------------|----------------------------------------------|--|

| R4 ← NOT R2               | R4 = R2'                                     |  |

| R5 ← NOT R3               | R5 = R3'                                     |  |

| R1 ← R4 AND R5            | R1 = R2' AND R3'                             |  |

| R1 ← NOT R1               | <b>R1</b> = (R2' AND R3')' = <b>R2 OR R3</b> |  |

#### **Used Only AND and NOT Operations!**

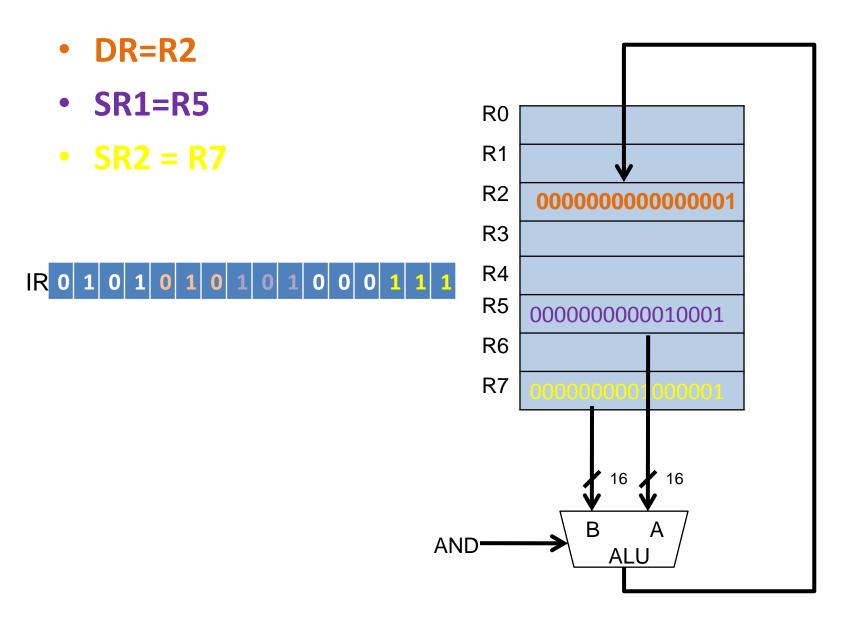

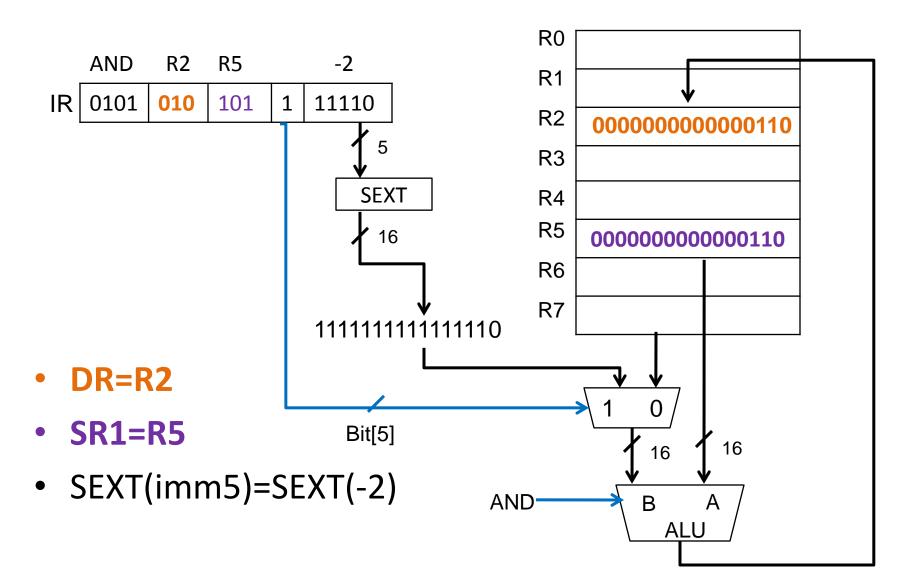

#### LC-3: AND Instructions

eservice and a

set NZP

set NZP

DR ← SR1 AND SR2;

$DR \leftarrow SR1 AND SEXT(imm5);$

AND<sup>+</sup>

DR 00 SR2 0101 SR1 0  $AND^+$ 0101 DR SR1 imm5

• OPCODE = 0101

- If bit[5] is zero − DR ← SR1 AND SR2 ~ 'register value'

- Else

− DR ← SR1 AND SEXT(imm5) ~ 'immediate'

Setcc() (means set N, Z and P based on in DR)

|                  | 15 14 13 12 | 11 10 9     | 8765          | 543210              |                                                                                             |

|------------------|-------------|-------------|---------------|---------------------|---------------------------------------------------------------------------------------------|

| $ADD^+$          | 0001        | DR          | SR1 (         | 0 00 SR2            | DR ← SR1 + SR2;<br>set NZP                                                                  |

| $ADD^+$          | 0001        | DR          | SR1           | 1 imm5              | $DR \leftarrow SR1 + SEXT(imm5);$                                                           |

| $AND^+$          | 0101        | DR          | SR1 (         | 0 00 SR2            | DR ← SR1 AND SR2;<br>set NZP                                                                |

| $AND^+$          | 0101        | DR          | SR1           | 1 imm5              | DR ← SR1 AND SEXT(imm5);<br>set NZP                                                         |

| BR               | 0000        | n z p       |               | PCoffset9           | IF $((n \cdot N) + (z \cdot Z) + (p \cdot P))$<br>THEN PC $\leftarrow$ PC + SEXT(PCoffset9) |

| JMP              | 1100        | 000         | BaseR         | 000000              | PC ← BaseR                                                                                  |

| JSR              | 0100        | 1           | PCoffset11    |                     | $R7 \leftarrow PC$<br>PC $\leftarrow PC + SEXT(PCoffset11)$                                 |

| JSRR             | 0100        | 0 00        | BaseR         | 000000              | R7 ← PC<br>PC ← BaseR                                                                       |

| $LD^+$           | 0010        | DR          |               | PCoffset9           | DR ← M[PC + SEXT(PCoffset9)];<br>Set NZP                                                    |

| LDI <sup>+</sup> | 1010        | DR          | ı PCoffset9   |                     | DR ← M[M[PC + SEXT(PCoffset9)]];<br>Set NZP                                                 |

| LDR <sup>+</sup> | 0110        | DR          | BaseR         | offset6             | DR ← M[BaseR + SEXT(offset6)];<br>Set NZP                                                   |

| LEA <sup>+</sup> | 1110        | DR          | PCoffset9     |                     | DR ← PC + SEXT(PCoffset9);<br>Set NZP                                                       |

| NOT <sup>+</sup> | 1001        | DR          | SR            | 111111              | DR ← NOT(SR);<br>Set NZP                                                                    |

| RET              | 1100        | 000         | 111           | 000000              | PC ← R7                                                                                     |

| ST               | 0011        | SR          | PCoffset9     |                     | M[PC + SEXT(PCoffset9)] ← SR                                                                |

| STI              | 1011        | SR          |               | PCoffset9           | M[M[PC + SEXT(PCoffset9)]] ← SR                                                             |

| STR              | 0111        | SR          | BaseR         | offset6             | $M[BaseR + SEXT(offset6)] \leftarrow SR$                                                    |

|                  | superscri   | pt "+" deno | tes instructi | ons that update the | Condition bits NZP                                                                          |

#### Example: R2 ← R5 AND R7

####

#### Example

- Initial Values

- R4 = x4444, R6 = x0876

- LC-3 Instruction:

- Address = x3101, Instruction: ADD R4, R6, #(-5)

- Give binary encoding of the LC-3 instruction:

- (ADD, DR, SR1, 1, imm5) = 0001 100 110 1 11011

- Give the value of R4 after execution of the instruction:

- -(x0876 + (-5)) = x0871

#### A Program Example

- Sum the numbers from 3 down to 1

- Store the result in memory location whose address is contained in R7

| A | Address | Opcode | Operands   | Comments   |

|---|---------|--------|------------|------------|

| 3 | 3000    | AND    | R1, R1, #0 | % CLEAR R1 |

|   |         |        |            |            |

|   |         |        |            |            |

|   |         |        |            |            |

|   |         |        |            |            |

|   |         |        |            |            |

|   |         |        |            |            |

|   |         |        |            |            |

|   |         |        |            |            |

## A Program Example: Register Status

- R1 running sum, R2 # to be added,

- R7 ptr to memory

| Address | Opcode | Operands    | R1 | R2 | Comments                               |

|---------|--------|-------------|----|----|----------------------------------------|

| 3000    | AND    | R1, R1, #0  | 0  | Х  | % CLEAR R1                             |

| 3001    | ADD    | R2, R1, #3  | 0  | 3  | % LOAD 3 INTO R2                       |

| 3002    | ADD    | R1, R1, R2  | 3  | 3  | % ADD CURRENT # TO<br>RUNNING SUM (R1) |

| 3003    | ADD    | R2, R2, #-1 | 3  | 2  | %DECREMENT # TO BE<br>ADDED            |

| 3004    | BRp    | #-3         | 3  | 2  | % IF R2>0 THEN REPEAT                  |

| 3005    | STR    | R1, R7, #0  |    |    | %STORE RESULT IN M[R7+0]               |

#### From Assembly Instructions to Binary Instructions

| Address | Assembly<br>Instruction | Register Transfer<br>Language                           | Bin y Instruction    |

|---------|-------------------------|---------------------------------------------------------|----------------------|

| 3000    | AND R1, R1, #0          | PC $\leftarrow$ PC+1;<br>R1 $\leftarrow$ 0              | 0101 001 001 1 00000 |

| 3001    | ADD R2, R1, #3          | PC ← PC+1;<br>R2 ← R1 + #3                              | 0001 010 001 1 00011 |

| 3002    | ADD R1, R1, R2          | PC ← PC+1;<br>R1 ← R1 + R2                              | 0001 001 001 0 00010 |

| 3003    | ADD R2, R2, #-1         | PC ← PC+1;<br>R2 ← R2 -1                                | 0001 010 010 1 11111 |

| 3004    | BRp #-3                 | (PC $\leftarrow$ PC+1)<br>PC $\leftarrow$ PC + SEXT(-3) | 0000 001 111 1 11101 |

| 3005    | STR R1, R7, #0          | PC ← PC+1;<br>M[R7+0] <- R1                             | 0111 001 111 0 00000 |