# ECE290 Fall 2012 Lecture 21

Dr. Zbigniew Kalbarczyk

## Today

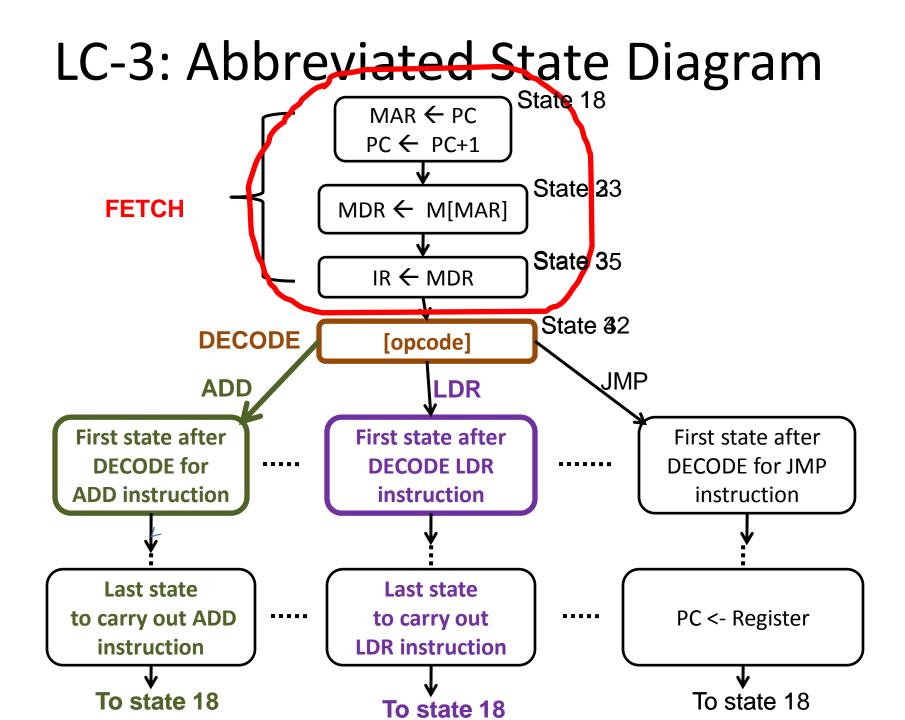

- LC -3 Instruction Cycle

- LC-3 State Diagram

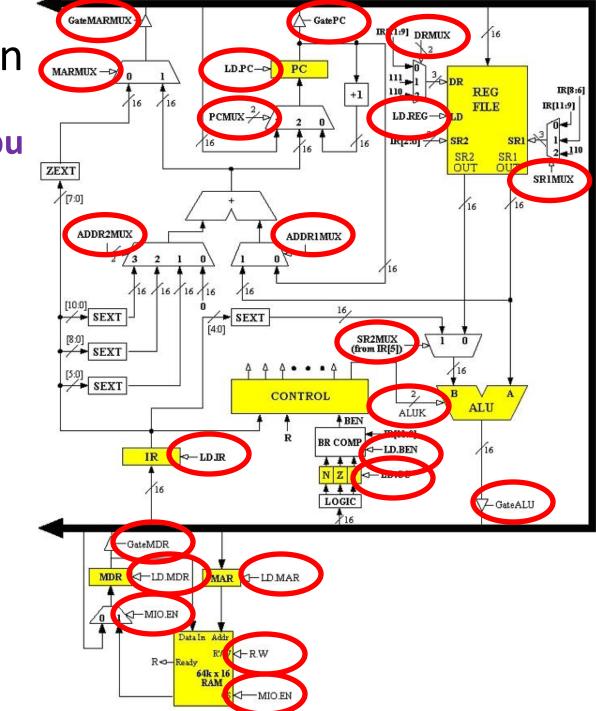

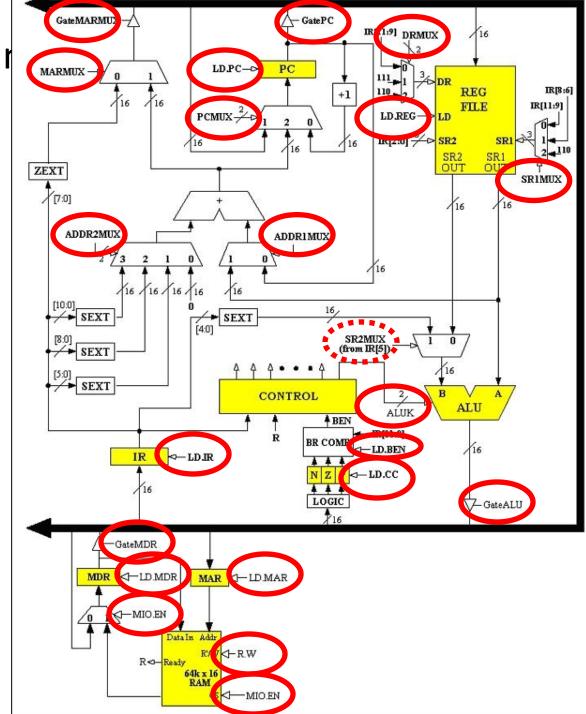

- Location of Control Signals in LC-3

- Values of Control Signals in LC-3 for ADD operation

- Values of Control Signals in LC-3 for NOT operation

### Instruction Cycle

#### **Phases of Instruction Cycle:**

- Fetch Phase:

- Fetch word from memory into instruction register (IR)

- Decode Phase:

- Decode word in IR as instruction

- Execute Phase

- Execute instruction

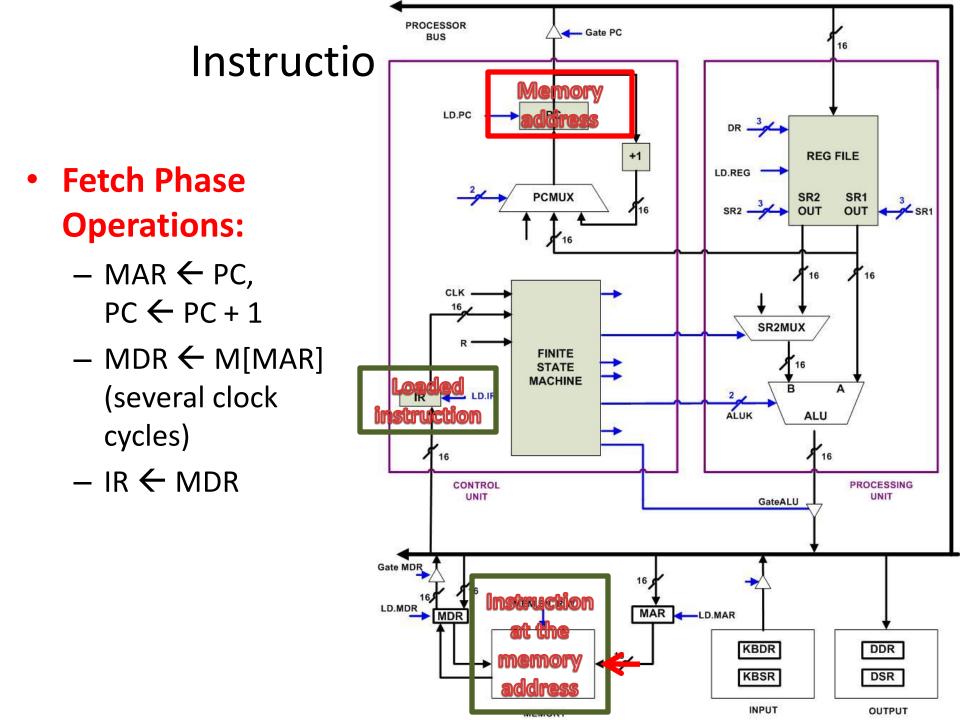

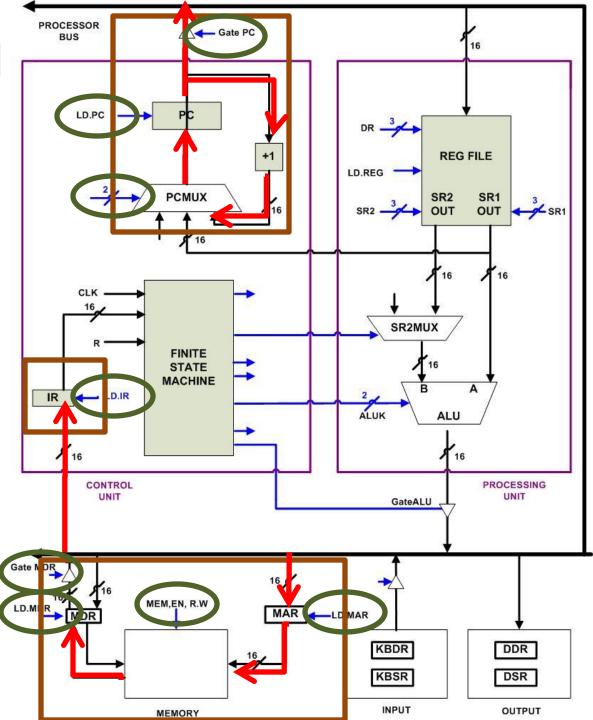

### Instruction Cycle: Fetch Phase

- Fetch Phase: fetch word from memory into IR

- Place memory address in PC on the bus and load MAR with the memory address

- –Increment PC

- Read from memory address specified in MAR to MDR

- -Copy MDR into IR

#### Instruction Cycle: Decode Phase

- **Decode Phase:** decode word in IR as instruction

- Evaluate address

- Fetch operands

- Use opcode to determine next state of control unit

- Example: ADD operation next state is 1 (PC will be PC+1)

#### Instruction Cycle: Execute Phase

- **Execute Phase:** execute instruction

- Move data across data path to function unit

- Activate function unit (includes Arithmetic/Logic Unit (ALU))

- Set status bits (condition codes)

- Store results

- **Example:** ADD  $\sim$  R4  $\leftarrow$  R5 + R6

- Control signals to move R5, R6 to ALU

- Control signals to compute addition

- Set NZP

- Control signals to move the result from ALU to R4

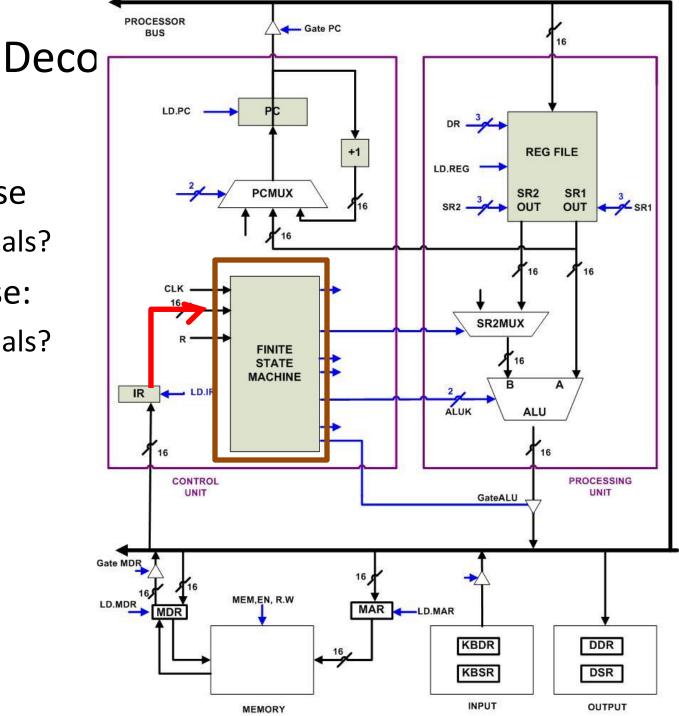

## Fetch Word

- Wanted: Move bits and words at the right time and to/from the right locations

- Fetch phase

- Control signals?

- Decode phase

Control signals?

- Execute phase:

- Control signals?

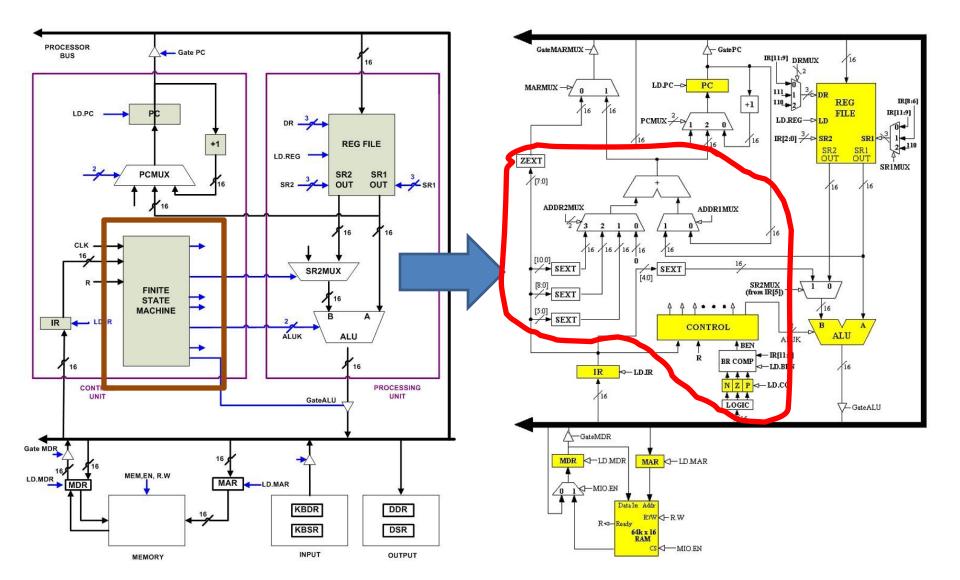

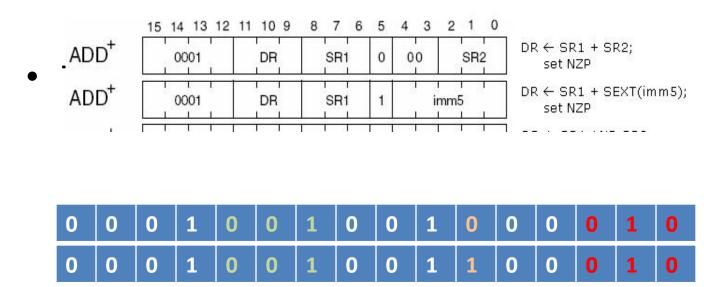

#### Design of Finite State Machine

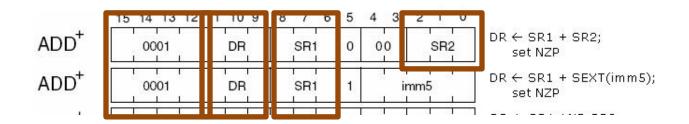

|              |                  | 15 14 13 1 | 11 10 9      | 76543210                         |                                                                                        |

|--------------|------------------|------------|--------------|----------------------------------|----------------------------------------------------------------------------------------|

|              | $ADD^+$          | 0001       |              | SR1 0 00 SR2                     | DR ← SR1 + SR2;<br>set NZP                                                             |

|              | $ADD^+$          | 0001       | DR           | SR1 1 imm5                       | DR ← SR1 + SEXT(imm5);<br>set NZP                                                      |

|              | $AND^+$          | 0101       |              | SR1 0 00 SR2                     | DR ← SR1 AND SR2;<br>set NZP                                                           |

|              | $AND^+$          | 0101       | DR           | SR1 1 imm5                       | $DR \leftarrow SR1 AND SEXT(imm5);$<br>set NZP                                         |

| Where is the | BR               | 0000       | n z p        | PCoffset9                        | IF ((n·N)+(z·Z)+(p·P))<br>THEN PC ← PC + SEXT(PCoffset9)                               |

| Wanted: deco | JMP              | 1100       | 000          | BaseR 000000                     | $PC \leftarrow BaseR$                                                                  |

|              | JSR              | 0100       | 1            | PCoffset11                       | $\begin{array}{l} R7 \leftarrow PC \\ PC \leftarrow PC + SEXT(PCoffset11) \end{array}$ |

|              | JSRR             | 0100       | 0 00         | BaseR 000000                     | $\begin{array}{l} R7 \leftarrow PC \\ PC \leftarrow BaseR \end{array}$                 |

|              | $LD^+$           | 0010       | DR           | PCoffset9                        | DR ← M[PC + SEXT(PCoffset9)];<br>Set NZP                                               |

|              | LDI <sup>+</sup> | 1010       |              | I PCoffset9                      | DR ← M[M[PC + SEXT(PCoffset9)]];<br>Set NZP                                            |

|              | $LDR^+$          | 0110       | DR           | BaseR offset6                    | $DR \leftarrow M[BaseR + SEXT(offset6)];$<br>Set NZP                                   |

|              | $LEA^+$          | 1110       | DR           | PCoffset9                        | DR ← PC + SEXT(PCoffset9);<br>Set NZP                                                  |

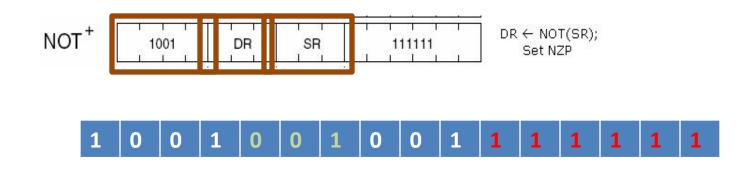

|              | NOT <sup>+</sup> | 1001       | DR           | SR 111111                        | DR ← NOT(SR);<br>Set NZP                                                               |

|              | RET              | 1100       | 000          | 111 000000                       | $PC \leftarrow R7$                                                                     |

|              | ST               | 0011       | SR           | PCoffset9                        | $M[PC + SEXT(PCoffset9)] \leftarrow SR$                                                |

|              | STI              | 1011       | SR           | PCoffset9                        | $M[M[PC + SEXT(PCoffset9)]] \leftarrow SR$                                             |

|              | STR              | 0111       | SR           | BaseR offset6                    | $M[BaseR + SEXT(offset6)] \leftarrow SR$                                               |

|              |                  | cuporcor   | int "+" deno | tes instructions that undate the | condition hits NZP                                                                     |

superscript "+" denotes instructions that update the condition bits NZP

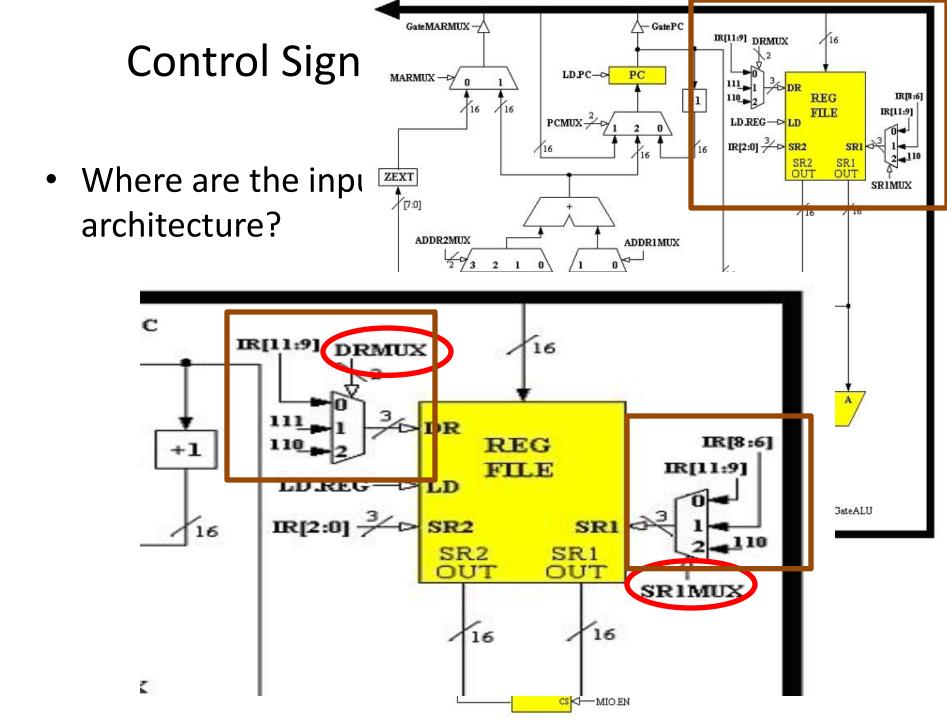

### **Decoding Operands**

#### Where is the operand?

#### Wanted: decode operand addresses and values

- Direct Decode: SR2 input: IR[2:0]

- Need MUX:

- SR1 input: IR[11:9] or IR[8:6] or 110

- DR input: IR[11:9] or 111 or 110

- Note:

- R6 (110) ~ stack pointer

- R7 (111) ~ used for subroutine calls

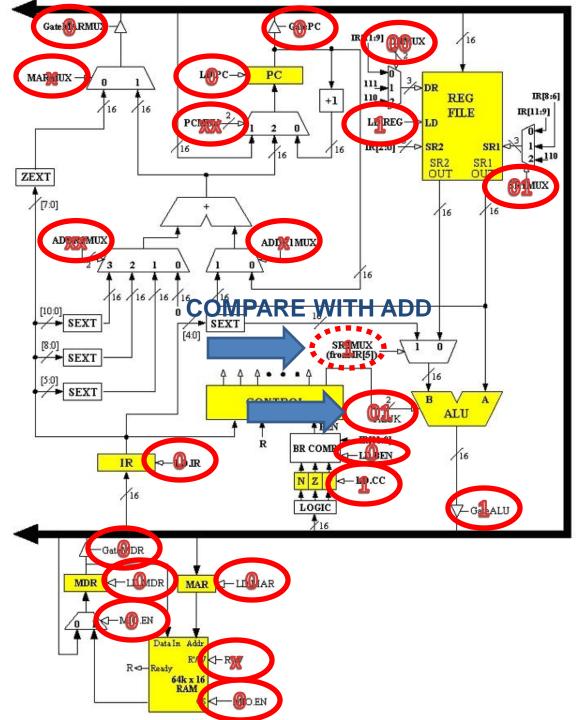

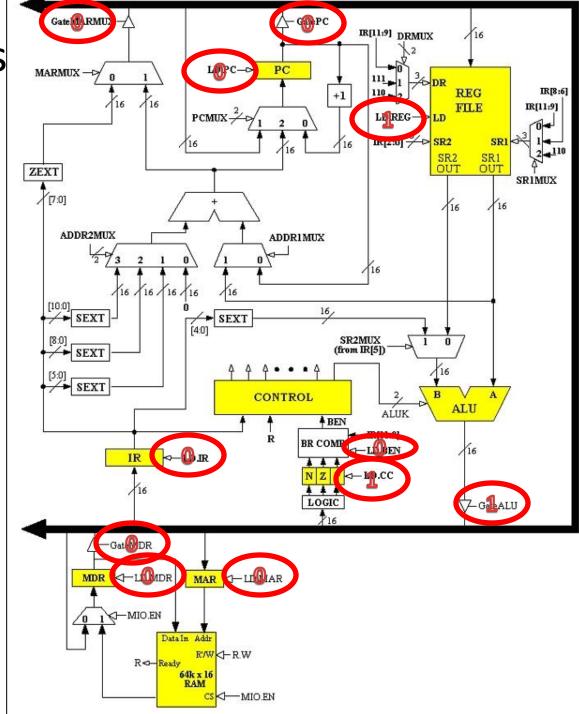

**Control Sign**

• Where are all **inpu** architecture?

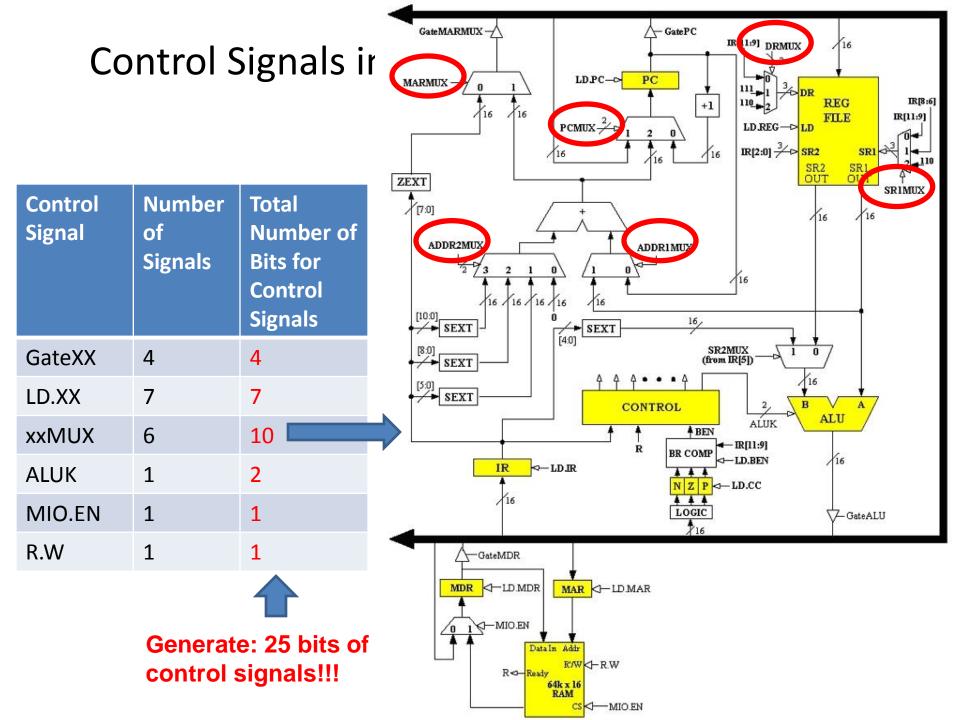

#### Control Signals ir

- Summary:

- GateXX: 4

- LD.XX: 7

- xxMUX: 6 (+1 IR[5])

- ALUK: 1

- MIO.EN: 1

- R.W: 1

#### **Execute Phase: ADD Operation**

- Task: execute ADD (1 microinstruction)

- SR1 (DR)  $\leftarrow$  SR1 + SR2, Load NZP

- SR1 (DR)  $\leftarrow$  SR1 + #2, Load NZP

# What are the control signals needed for the execution of the microinstruction?

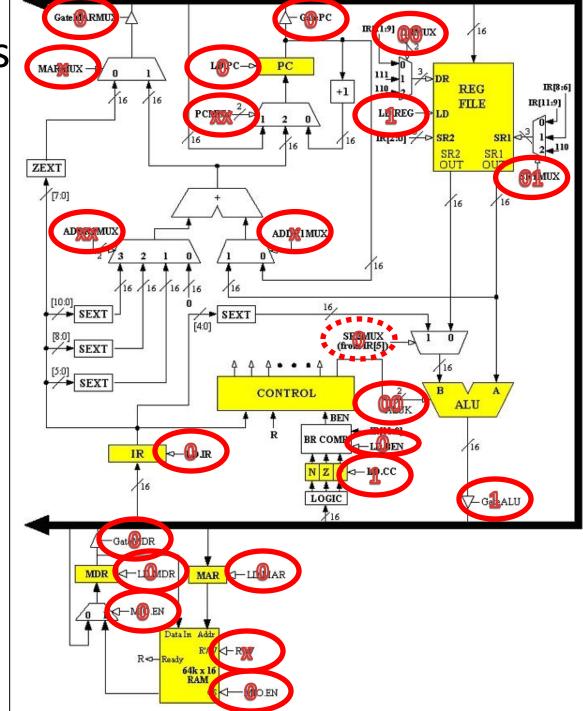

#### Execute Phase: ADD Operation – Bus Gate Signals

• Task: SR1 (DR) ← SR1 + SR2, Load NZP

#### n

- GateXX:

- GatePC=0

- GateMARMUX = 0

- GateMDR = 0

- GateALU = 1

| Control<br>Signal | Number of<br>Signals | Total Number<br>of Bits for<br>Control Signals |

|-------------------|----------------------|------------------------------------------------|

| GateXX            | 4                    | 4                                              |

| LD.XX             | 7                    | 7                                              |

| xxMUX             | 6                    | 10                                             |

| ALUK              | 1                    | 2                                              |

| MIO.EN            | 1                    | 1                                              |

| RW                | 1                    | 1                                              |

Execute Phase: ADD Operation – Load signals

• Task: SR1 (DR) ← SR1 + SR2, Load NZP

####

- LD.XX:

- LD.PC=0

- LD.BEN = 0

- LD.MAR = 0

- LD.MDR = 0

- LD.IR=0

- LD.REG =1

- LD.CC = 1

| Control<br>Signal | Number of<br>Signals | Total Number<br>of Bits for<br>Control Signals |

|-------------------|----------------------|------------------------------------------------|

| GateXX            | 4                    | 4                                              |

| LD.XX             | 7                    | 7                                              |

| xxMUX             | 6                    | 10                                             |

| ALUK              | 1                    | 2                                              |

| MIO.EN            | 1                    | 1                                              |

| RW                | 1                    | 1                                              |

# **Control Signals**

- Current Assignment of Control Signals:

- GateXX:

- LD.XX:

#### Execute Phase: ADD Operation – Multiplexer Selection Signals

• Task: SR1 (DR) ← SR1 + SR2, Load NZP

0 0 1 0 1 0 1 0 1 0 0 1 0 0 1 0 0 0 0 1 0

- Control signals:

- xxMUX:

- SR1MUX = 01 (IR[8:6])

- DRMUX = 00 (IR[11:9])

- MARMUX =x

- PCMUX =x

- ADDR1MUX =x

- ADDR2MUX=x

Control Number of **Total Number** Signal Signals of Bits for **Control Signals** GateXX 4 4 7 LD.XX 7 **xxMUX** 6 10 ALUK 2 1 MIO.FN 1 1 RW 1 1

SR2MUX=IR[5] = 0

# Execute Phase: ADD Operation – Other Control Signals

• Task: SR1 (DR) ← SR1 + SR2, Load NZP

- Control signals:

- ALUK = 00

- MIO.EN =0

-RW = x

| Control<br>Signal | Number of<br>Signals | Total Number<br>of Bits for<br>Control Signals |

|-------------------|----------------------|------------------------------------------------|

| GateXX            | 4                    | 4                                              |

| LD.XX             | 7                    | 7                                              |

| xxMUX             | 6                    | 10                                             |

| ALUK              | 1                    | 2                                              |

| MIO.EN            | 1                    | 1                                              |

| RW                | 1                    | 1                                              |

# **Control Signals**

- All Assignments of Control Signals:

- GateXX:

- LD.XX:

- xxMUX:

- ALUK:

- MIO.EN:

- R.W:

# **Control Signals**

- Selections based on control signals:

- SR1 selected based on IR[8:6]

- SR2 selected based on IR[2:0]

- DR selected based on IR[11:9]

- What to add selected based on IR[5]

# Execute Phase: ADD Operation – Summary of Control Signals

| Signal<br>Name | Binary Value | Signal<br>Name | Binary Value | Signal Name | Binary<br>Value |

|----------------|--------------|----------------|--------------|-------------|-----------------|

| GateMAR 0      | 0            | LD.BEN         | 0            | MARMUX      | Х               |

| MUX            |              | LD.MAR         | 0            | PCMUX       | ХХ              |

| GateMDR        | 0            | LD.MDR         | 0            | ADDR1MUX    | х               |

| GateALU        | 1            | LD.IR          | 0            | ADDR2MUX    | XX              |

| GatePC         | 0            | LD.PC          | 0            | DRMUX       | 00              |

| Signal         | Binary Value | LD.REG         | 1            | SR1MUX      | 01              |

| Name           |              | LD.CC          | 1            |             |                 |

| ALUK           | 00           |                |              |             |                 |

MIO.EN

R.W

0

Х

### LC-3 Control Word Fields

no Interrupt or Exception Control signals!

|                |        |                   |                |                 |                                        |                          | Signal Name                             | Binary                |                 |

|----------------|--------|-------------------|----------------|-----------------|----------------------------------------|--------------------------|-----------------------------------------|-----------------------|-----------------|

|                |        |                   | Signal<br>Name | Binary<br>Value | Signal<br>Name                         | Binary<br>Value          |                                         | Value                 |                 |

|                |        | i                 | LD.BEN         | 0               |                                        |                          | MARMUX                                  | Х                     |                 |

|                |        |                   | LD.MAR         | 0               | GateMAR<br>MUX                         | 0                        | PCMUX                                   | ХХ                    |                 |

|                |        |                   | LD.MDR         | 0               | GateMDR                                | 0                        | ADDR1MUX                                | х                     |                 |

|                |        |                   | LD.IR          | 0               | CataAll                                | 1                        | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | ~                     |                 |

|                |        |                   | LD.PC          | 0               | GateALU                                | 1                        | ADDR2MUX                                | X Signal<br>Name      | Binary<br>Value |

|                |        |                   | LD.REG         | 1               | GatePC                                 | 0                        | DRMUX                                   |                       | 00              |

|                |        |                   | LD.CC          | 1               | X                                      |                          |                                         |                       |                 |

|                |        |                   |                |                 | JC<br>JC                               |                          | SR1MUX                                  | <sup>0</sup> MIO.EN   | 0               |

|                | [2:0]  |                   | zα             | с<br>с          | ARA J                                  |                          | л л<br>М Л                              | R.W                   | Х               |

| _              |        | <u>.</u>          | BEN            | D H C H         | te M <sup>1</sup><br>te M <sup>1</sup> | GatePO<br>MARMU<br>POMUX | ADDR1MU<br>ADDR2MU<br>DRMUX             | UK<br>UK<br>UK        | i<br>N >        |

|                | ŏ      | J[5               | <u>è</u> è     | 9999            | a n n<br>o o o o                       | Ω A A<br>POI             | AD<br>AD<br>AD                          | SR1M<br>ALUK<br>MTO E | 2.2             |

| For a given 10 | contro | ol signa          | als 🗲          |                 |                                        | 1-X                      |                                         |                       |                 |

| pro pro        | ovided | by the<br>lock cy |                |                 | 25                                     | contro                   | l signals                               |                       |                 |

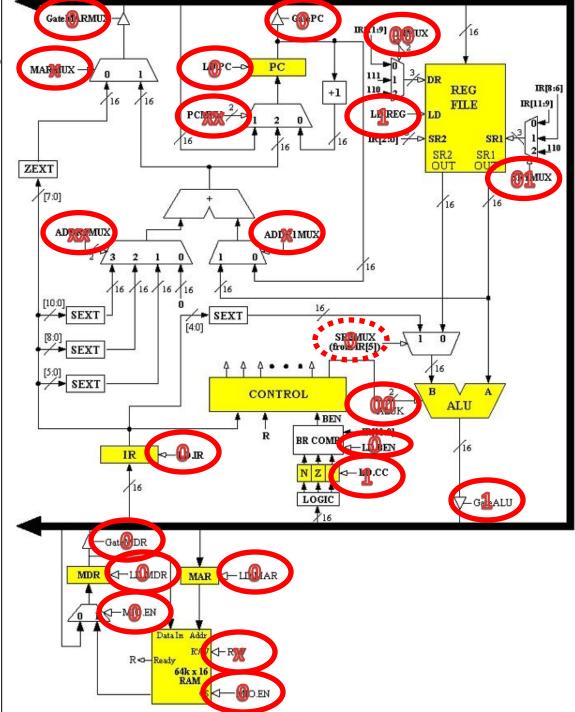

#### **Execute Phase: NOT Operation**

• Task: SR1 (DR) ← NOT (SR1), Load NZP

- Directly derived control signals:

- SR2MUX=1 (IR[5])

- SR1MUX = 01 (IR[8:6])

- DRMUX = 00 (IR[11:9])

# Execute Phase: NOT Operation – Summary of Control Signals

• Control signals

R.W

Х

| Signal<br>Name | Binary Value | Signal<br>Name | Binary Value | Signal Name | Binary<br>Value |

|----------------|--------------|----------------|--------------|-------------|-----------------|

| GateMAR        | 0            | LD.BEN         | 0            | MARMUX      | Х               |

| MUX            |              | LD.MAR         | 0            | PCMUX       | XX              |

| GateMDR        | 0            | LD.MDR         | 0            | ADDR1MUX    | Х               |

| GateALU        | 1            | LD.IR          | 0            | ADDR2MUX    | XX              |

| GatePC         | 0            | LD.PC          | 0            | DRMUX       | 00              |

| Signal         | Binary Value | LD.REG         | 1            | SR1MUX      | 01              |

| Name           |              | LD.CC          | 1            |             |                 |

| ALUK           | 10           |                |              |             |                 |

| MIO.EN         | 0            |                |              |             |                 |

# **Control Signals**

- Selections based on control signals:

- SR1 selected based on IR[8:6]

- DR selected based on IR[11:9]

- What to add selected based on IR[5]