# Silicon Technology Leadership for the Mobility Era

Mark Bohr, Intel Senior Fellow

SPCS008

## **Agenda**

- Transistor Scaling Trends

- 32 nm SoC Technology

- 22 nm CPU Technology

- 22 nm SoC Technology

The PDF for this Session presentation is available from our Technical Session Catalog at the end of the day at: intel.com/go/idfsessions

**URL** is on top of Session Agenda Pages in Pocket Guide

## **Agenda**

- Transistor Scaling Trends

- 32 nm SoC Technology

- 22 nm CPU Technology

- 22 nm SoC Technology

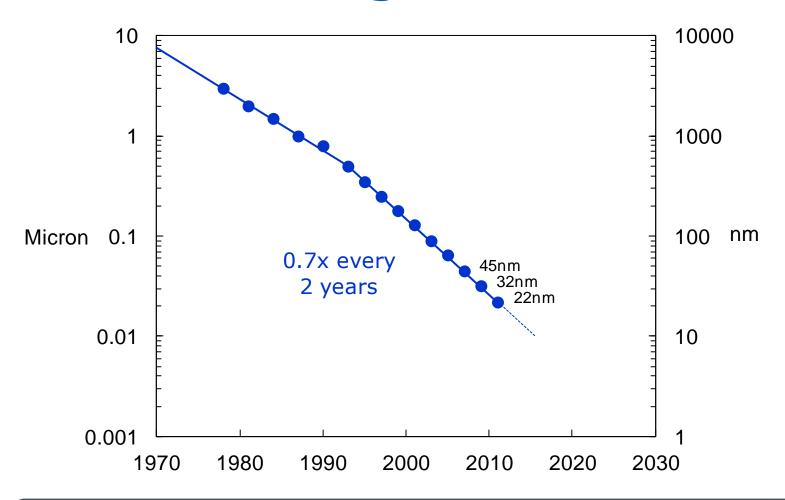

## **Transistor Scaling**

Transistor dimensions scale to improve performance, reduce power and reduce cost per transistor

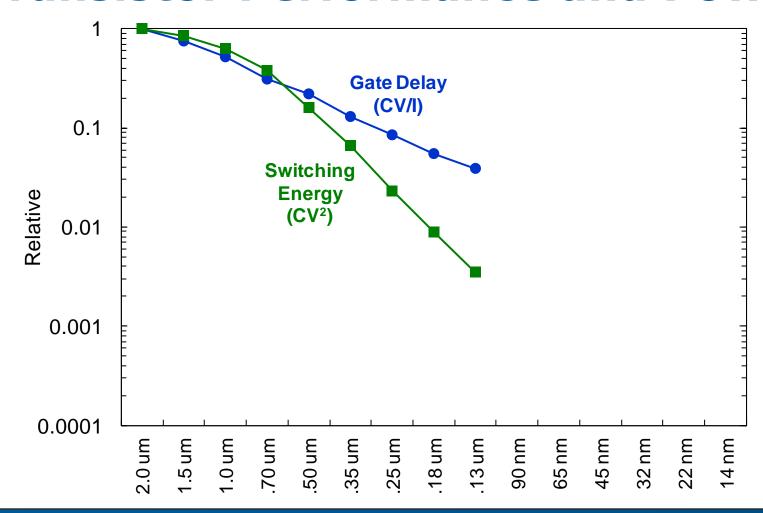

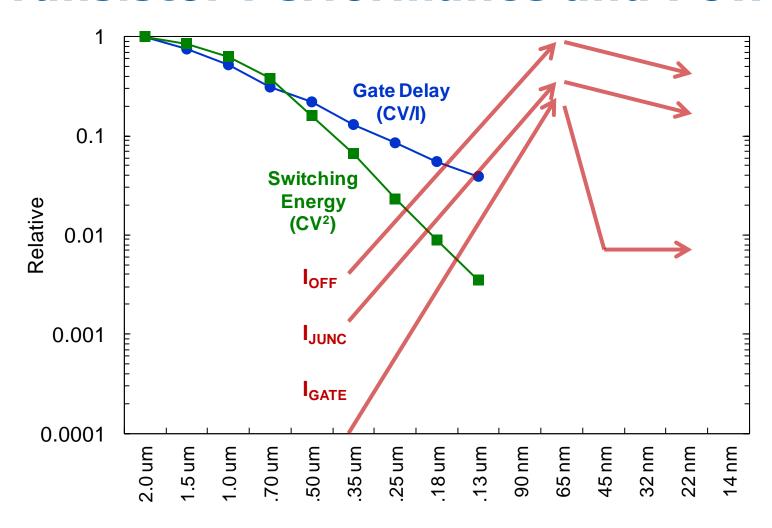

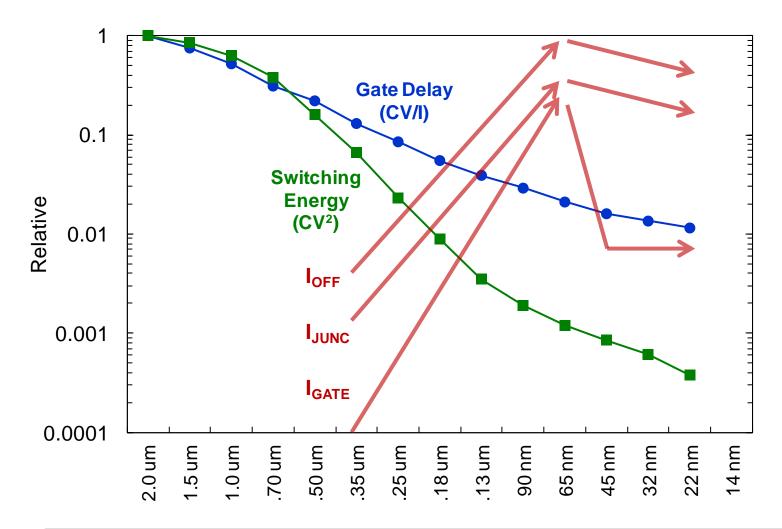

#### **Transistor Performance and Power**

"Classical" transistor scaling provided improvements in performance (gate delay) and active power (switching energy)

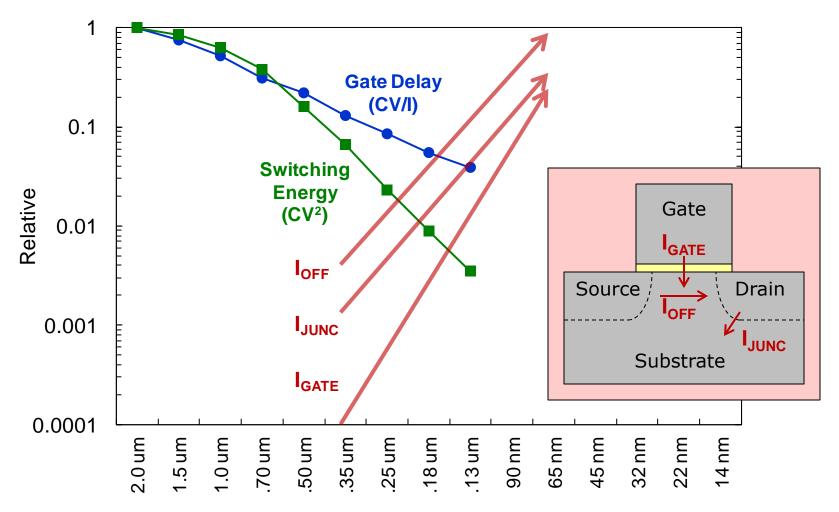

#### **Transistor Performance and Power**

... but at the expense of increased leakage current

## **Non-Classical Scaling**

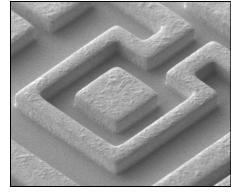

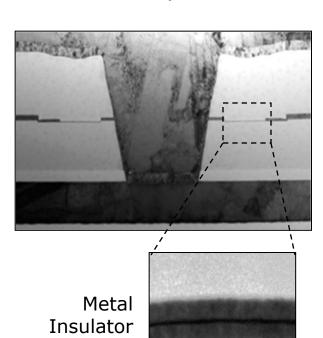

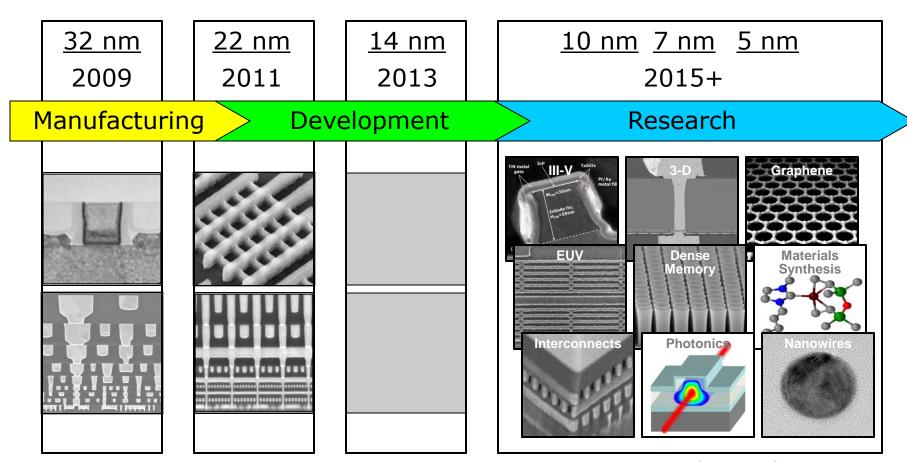

90 nm 2003 65 nm 2005 45 nm 2007 32 nm 2009 22 nm 2011

Strained Silicon

High-k Metal Gate

Tri-Gate

Scaling now requires continual innovations in transistor structure and materials

#### **Transistor Performance and Power**

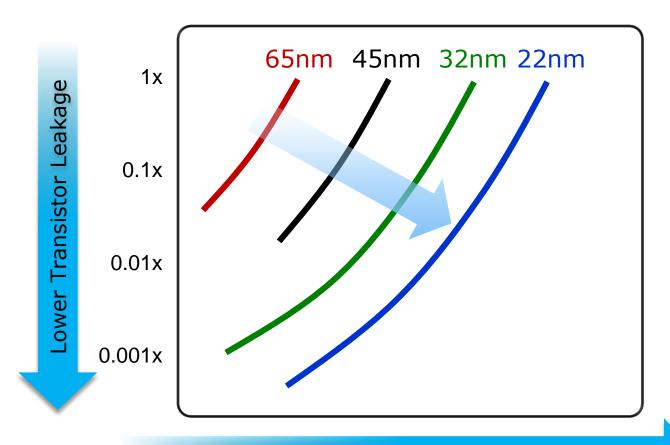

Transistor scaling now focuses on reducing leakage

#### **Transistor Performance and Power**

... and continues to improve performance and power

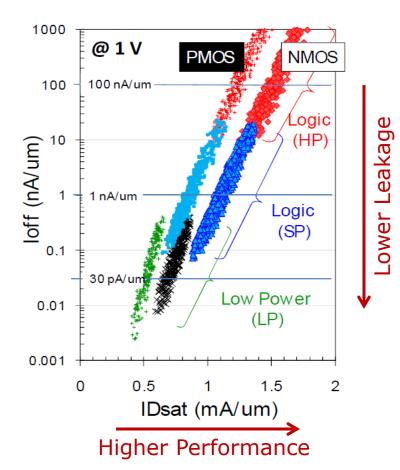

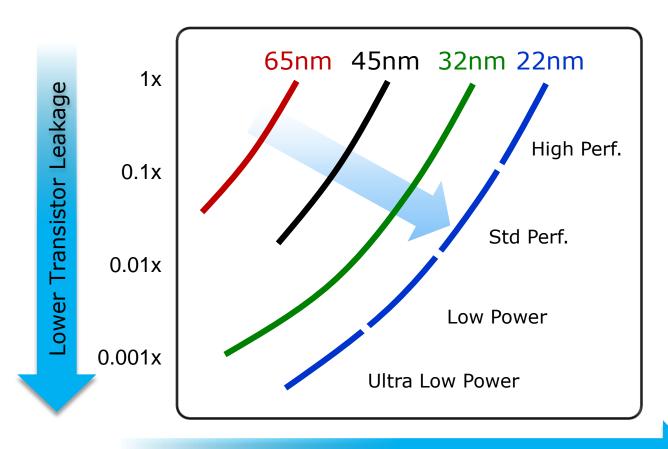

## **Transistor Performance vs. Leakage**

**Higher Transistor Performance (Switching Speed)**

Transistors now improve on both performance and leakage vectors

## **Transistor Performance vs. Leakage**

**Higher Transistor Performance (Switching Speed)**

Wider range of transistors to support a wider range of products

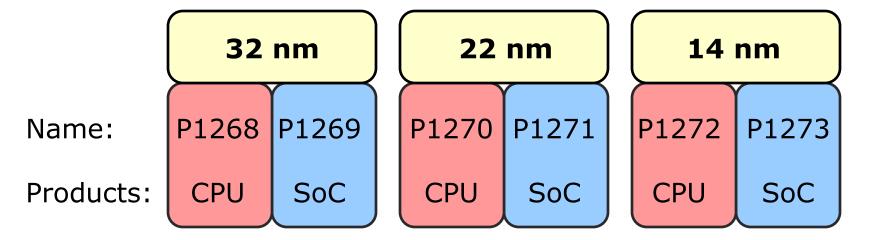

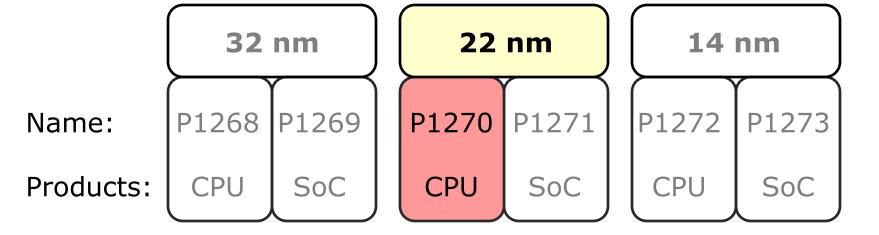

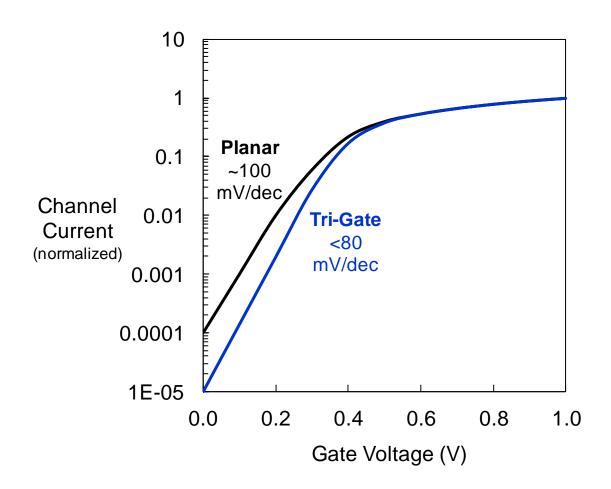

## Intel® Technology Roadmap

Intel develops both CPU and SoC versions of each generation

## Intel® Technology Roadmap

32 nm 22 nm 14 nm P1268 P1269 P1270 P1271 P1272 P1273 Name: CPU **Products:** CPU SoC SoC **CPU** SoC

Intel develops both CPU and SoC versions of each generation

## **Low Power Smartphone Products**

Medfield Phone

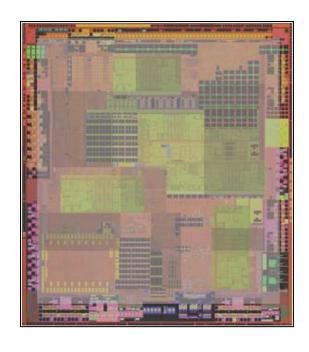

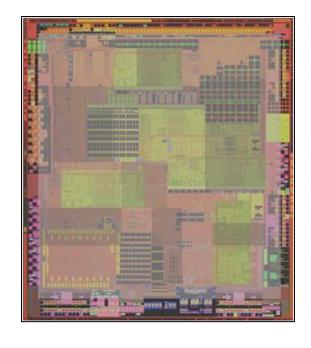

32 nm Intel® Atom™ processor (Medfield) SoC 432 million transistors, 64 mm²

## **Low Power Smartphone Products**

Intel Developer Forum, Sep. 2009

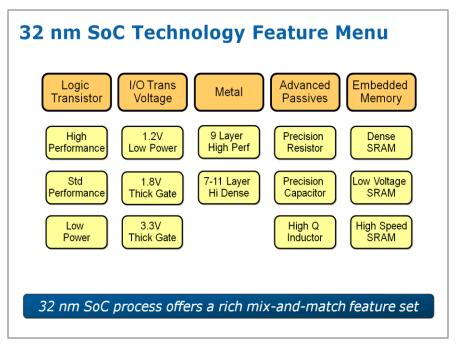

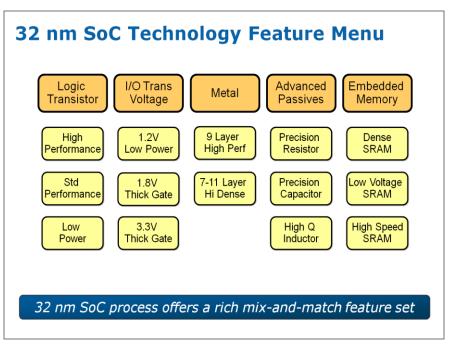

32 nm SoC Technology

32 nm Intel® Atom™ processor (Medfield) SoC 432 million transistors, 64 mm²

## **Low Power Smartphone Products**

Intel Developer Forum, Sep. 2009

32 nm SoC Technology

32 nm SoC transistors range from high performance to low power

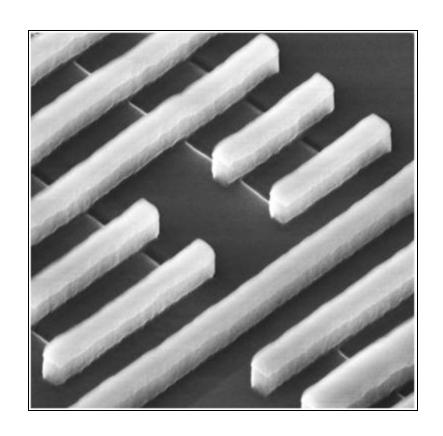

## Intel® Technology Roadmap

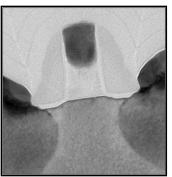

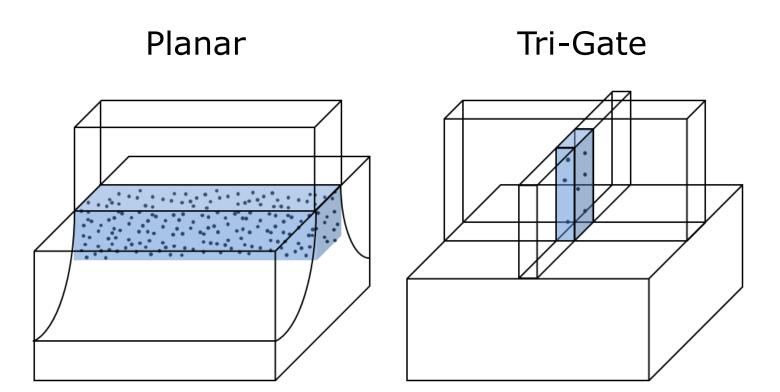

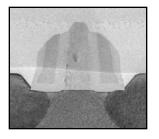

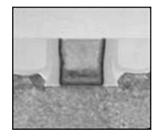

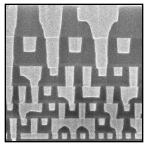

# **32 nm Planar Transistors**

# 22 nm Tri-Gate Transistors

22 nm generation introduces revolutionary 3-D Tri-Gate transistors

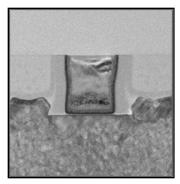

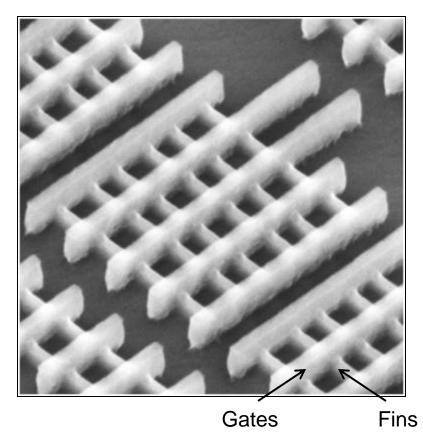

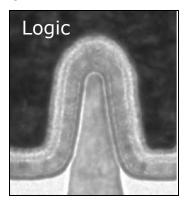

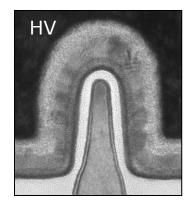

## **Fully Depleted Device**

Tri-Gate transistors are fully depleted devices offering a steeper sub-threshold slope

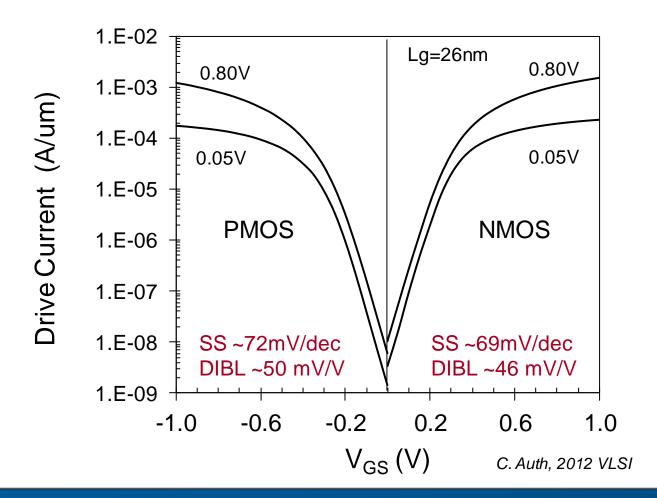

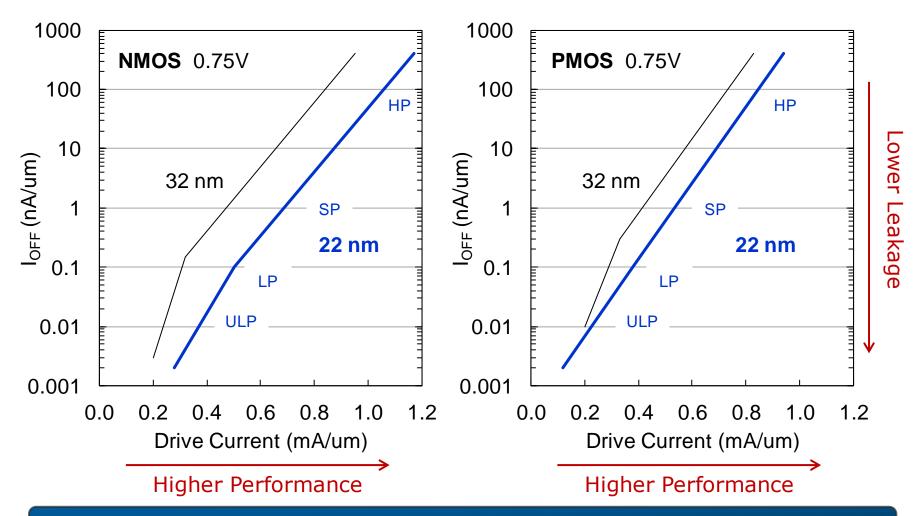

#### 22 nm Tri-Gate I-V Curves

Tri-Gate provides steepest sub-threshold slope and best short channel (DIBL) values of any technology in manufacturing

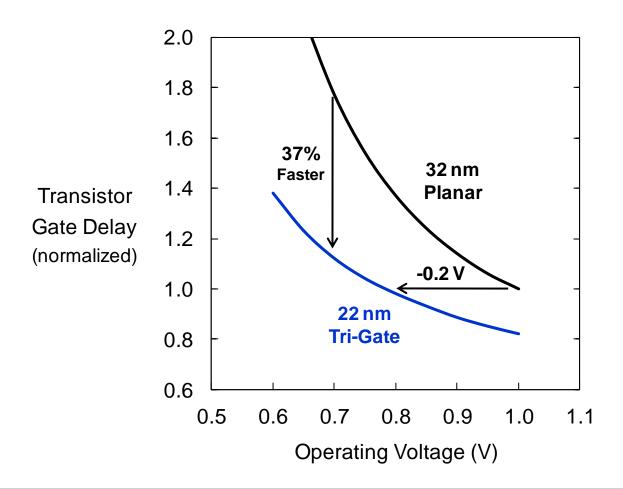

## **Performance/Power Benefits**

Tri-Gate provides 37% speed up at low voltage or 50% active power reduction at same performance

## **Reduced Channel Doping**

Fully depleted Tri-Gate structure has reduced channel doping, providing improved performance and reduced variability

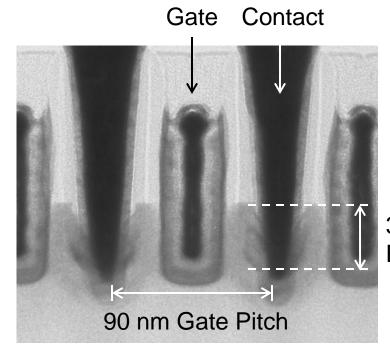

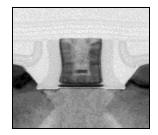

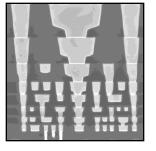

#### 22 nm Tri-Gate Transistors

34 nm

Fin Height

----8nm

Fin

Width

34 nm Fin Height

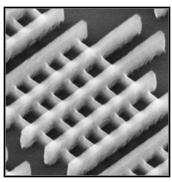

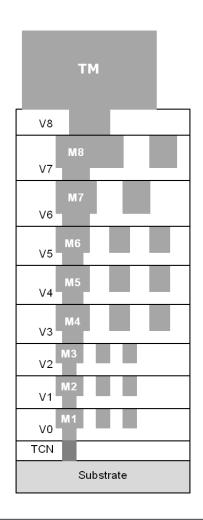

#### 22 nm Interconnects

| <u>Layer</u> | <u>Pitch</u> |  |  |  |

|--------------|--------------|--|--|--|

| TM           | 14 um        |  |  |  |

| M8           | 360 nm       |  |  |  |

| M7           | 320 nm       |  |  |  |

| M6           | 240 nm       |  |  |  |

| M5           | 160 nm       |  |  |  |

| M4           | 112 nm       |  |  |  |

| М3           | 80 nm        |  |  |  |

| M2           | 80 nm        |  |  |  |

| M1           | 90 nm        |  |  |  |

Minimum pitch scaled ~0.7x from 32 nm for ~2x transistor density improvement

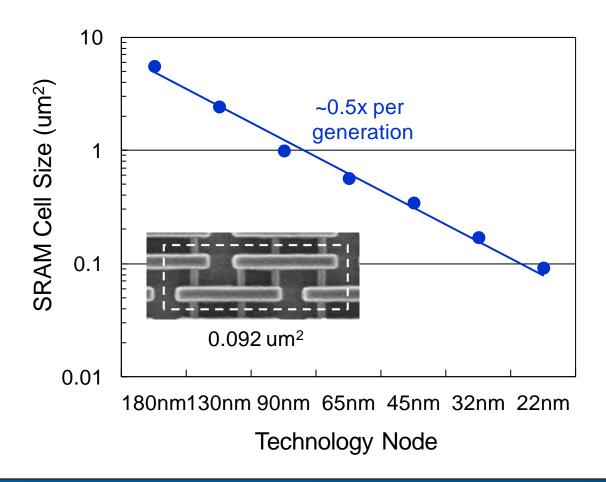

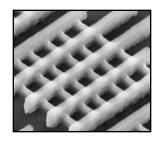

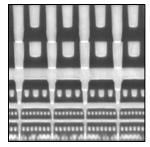

#### **SRAM Cells**

0.092 um<sup>2</sup> and 0.108 um<sup>2</sup> SRAM cells optimized for density and performance/power

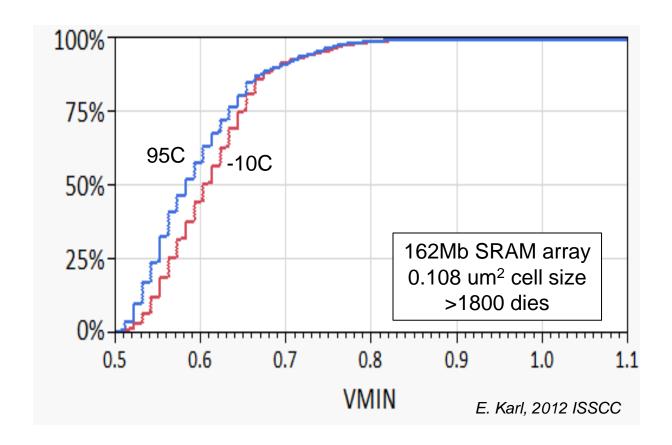

## **SRAM Array V<sub>MIN</sub>**

0.60V medium active  $V_{MIN}$  for low power applications

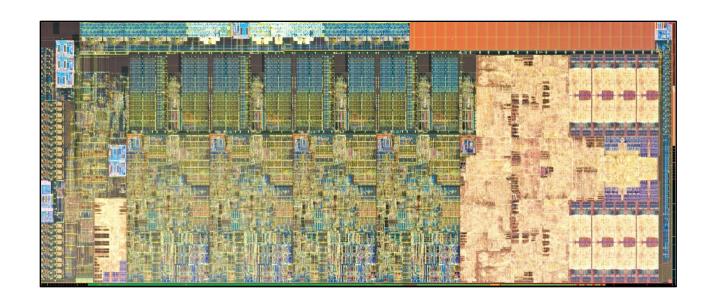

#### **3RD** Generation Intel® Core™ Processor

22 nm Tri-Gate Technology

4 Cores + Integrated Graphics

1.4 Billion Transistors, 160 mm<sup>2</sup>

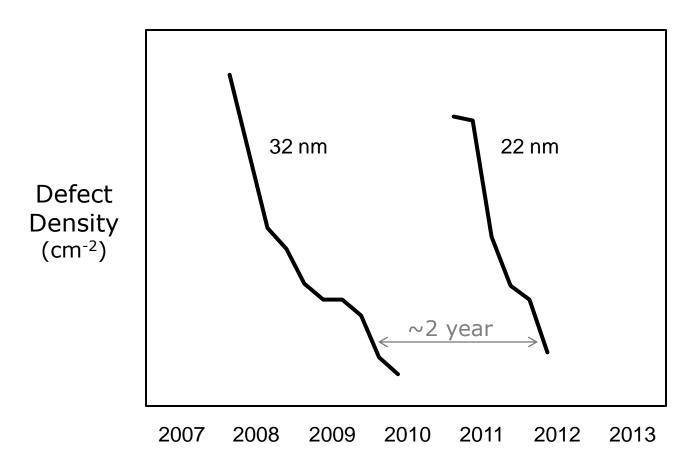

## 22 nm Defect Density Trend

22 nm defect density now at low levels needed for volume manufacturing

## 22 nm Manufacturing Fabs

D1D Oregon

✓

D1C Oregon

Fab 32 Arizona 🗸

Fab 28 Israel 🗸

Fab 12 Arizona

✓ In production 2Q '12

## Intel® Technology Roadmap

32 nm 22 nm 14 nm P1268 P1269 P1270 P1271 P1272 P1273 Name: **CPU** SoC CPU SoC CPU Products: SoC

## CPU vs. SoC Technology Comparison

#### **CPU (P1270)**

#### **SoC (P1271)**

#### **Similarities**

Tri-Gate Structure

Tight Transistor Pitch

Dense SRAM Cell

Lower Level Interconnects

Fab Process Equipment

#### Differences

Logic Transistors

I/O Transistors

Upper Level Interconnects

**Precision Passives**

Same

Same

Same

Same

Same

High Speed

Std Voltage

High Speed

None

Same

Same

Same

Same

Same

Low Leakage

Std and High Volt

Dense

R, C and L

## 22 nm SoC Technology Features

I/O Trans **Embedded** Logic **Passives** Metal Voltage **Transistor** Memory High Dense High 1.2V 8-11 Layer Precision Low Power Stacks **SRAM** Performance Resistor Std 1.8V MIM Low Voltage Performance Capacitor **SRAM** Thick Gate 3.3V High Q High Speed Low SRAM Thick Gate Inductor Power Ultra **HD OTP** e-Fuse Low Power

22 nm SoC technology offers a rich menu of feature options

## **Transistor Performance vs. Leakage**

Higher Transistor Performance (Switching Speed)

22 nm SoC technology offers a wide range of transistors

## **Transistor Performance vs. Leakage**

22 nm SoC technology offers a wide range of transistors

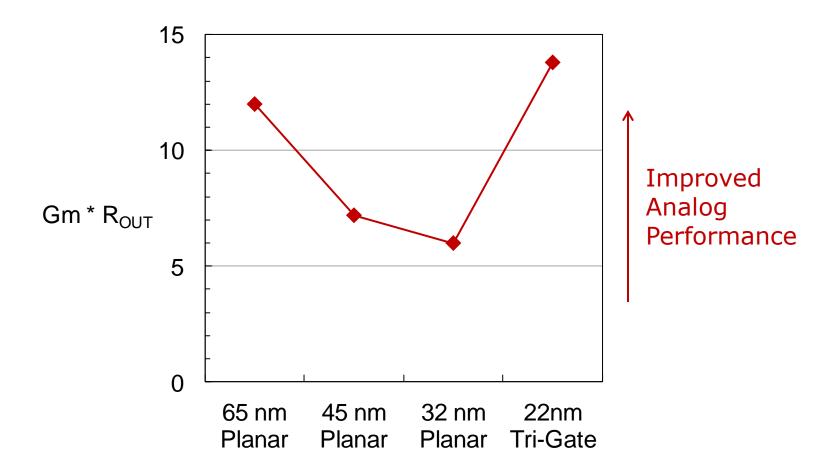

## **Analog Device Characteristics**

22 nm Tri-Gate transistors provide improved Gm \* R<sub>OUT</sub> for improved analog circuit performance

## 22 nm SoC Interconnect Options

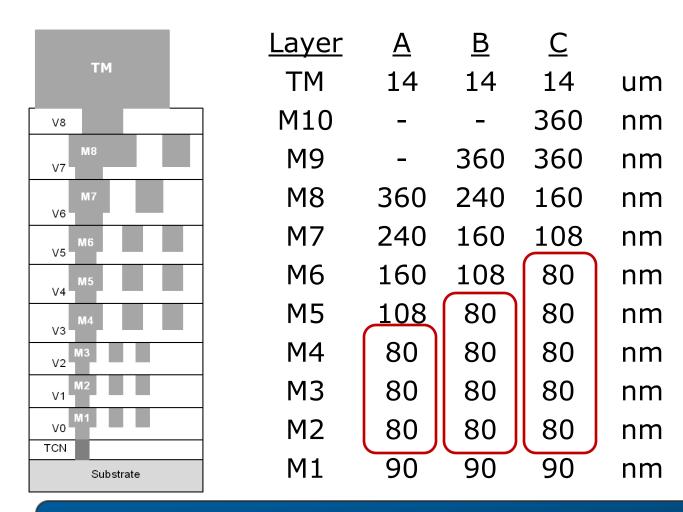

| <u>Layer</u> | <u>A</u> | <u>B</u> | <u>C</u> |    |

|--------------|----------|----------|----------|----|

| TM           | 14       | 14       | 14       | um |

| M10          | -        | -        | 360      | nm |

| M9           | -        | 360      | 360      | nm |

| M8           | 360      | 240      | 160      | nm |

| M7           | 240      | 160      | 108      | nm |

| M6           | 160      | 108      | 80       | nm |

| M5           | 108      | 80       | 80       | nm |

| M4           | 80       | 80       | 80       | nm |

| М3           | 80       | 80       | 80       | nm |

| M2           | 80       | 80       | 80       | nm |

| M1           | 90       | 90       | 90       | nm |

Range of SoC interconnect options for low cost or high density

## 22 nm SoC Interconnect Options

80 nm pitch is done with single patterning, thus an optimal pitch to use for this generation

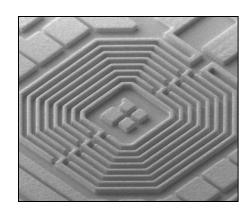

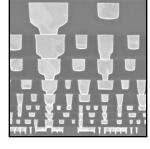

#### 22 nm SoC Device Features

High Voltage I/O Transistors

**Inductors**

MIM Capacitor

Metal

## 2 Year Technology Cycles

90 nm 2003

45 nm 2007 32 nm 2009 22 nm 2011

### **Innovation Enabled Technology Pipeline**

Future options subject to change

## Advantage of an Integrated Device Manufacturer

#### Research

#### Components Research

Equipment Vendors

Industry Consortia

Universities

Government Labs

Identify innovative technologies

## Advantage of an Integrated Device Manufacturer

#### Research

#### **Development**

Components Research Product Design

Logic Technology Development

Equipment Vendors

Industry Consortia

Universities

Government Labs

Design Tools Photo Masks Packaging

Identify innovative technologies

- Co-optimize process+product

- Design for manufacturing

## Advantage of an Integrated Device Manufacturer

Research

**Development**

**Manufacturing**

Components Research Product Design

Logic Technology Development Wafer Manufacturing Fabs

Equipment Vendors

Industry Consortia

Universities

Government Labs

Design Tools Photo Masks Packaging

Oregon Arizona New Mexico Israel Ireland China

Identify innovative technologies

- Co-optimize process+product

- Design for manufacturing

- Early product ramp

- Rapid yield learning

## **Summary**

- Transistor scaling continues to provide improvements in performance, power and cost, but now with greater focus on power reduction

- Scaling no longer follows a "classical" path and requires continued innovations in materials and structures

- A highly integrated approach is needed to successfully bring innovative technologies from the research phase to high volume manufacturing

- Low power System-on-Chip technologies are increasingly important to support the wide range of features needed on mobile computing devices

# Additional Sources of Information on This Topic:

More web based info:

www.intel.com/technology/architecture-silicon

#### **Legal Disclaimer**

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

- A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

- Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

- The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

- Intel product plans in this presentation do not constitute Intel plan of record product roadmaps. Please contact your Intel representative to obtain Intel's current plan of record product roadmaps.

- Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. Go to: http://www.intel.com/products/processor\_number.

- Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

- Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: <a href="http://www.intel.com/design/literature.htm">http://www.intel.com/design/literature.htm</a>

- Intel, Core, Ultrabook, Sponsors of Tomorrow and the Intel logo are trademarks of Intel Corporation in the United States and other countries.

- \*Other names and brands may be claimed as the property of others.

- · Copyright ©2012 Intel Corporation.

#### **Risk Factors**

The above statements and any others in this document that refer to plans and expectations for the second quarter, the year and the future are forward-looking statements that involve a number of risks and uncertainties. Words such as "anticipates," "expects," "intends," "plans," "believes," "seeks," "estimates," "may," "will," "should" and their variations identify forward-looking statements. Statements that refer to or are based on projections, uncertain events or assumptions also identify forward-looking statements. Many factors could affect Intel's actual results, and variances from Intel's current expectations regarding such factors could cause actual results to differ materially from those expressed in these forward-looking statements. Intel presently considers the following to be the important factors that could cause actual results to differ materially from the company's expectations. Demand could be different from Intel's expectations due to factors including changes in business and economic conditions, including supply constraints and other disruptions affecting customers; customer acceptance of Intel's and competitors' products; changes in customer order patterns including order cancellations; and changes in the level of inventory at customers. Uncertainty in global economic and financial conditions poses a risk that consumers and businesses may defer purchases in response to negative financial events, which could negatively affect product demand and other related matters. Intel operates in intensely competitive industries that are characterized by a high percentage of costs that are fixed or difficult to reduce in the short term and product demand that is highly variable and difficult to forecast. Revenue and the gross margin percentage are affected by the timing of Intel product introductions and the demand for and market acceptance of Intel's products; actions taken by Intel's competitors, including product offerings and introductions, marketing programs and pricing pressures and Intel's response to such actions; and Intel's ability to respond quickly to technological developments and to incorporate new features into its products. Intel is in the process of transitioning to its next generation of products on 22nm process technology, and there could be execution and timing issues associated with these changes, including products defects and errata and lower than anticipated manufacturing yields. The gross margin percentage could vary significantly from expectations based on capacity utilization; variations in inventory valuation, including variations related to the timing of qualifying products for sale; changes in revenue levels; segment product mix; the timing and execution of the manufacturing ramp and associated costs; start-up costs; excess or obsolete inventory; changes in unit costs; defects or disruptions in the supply of materials or resources; product manufacturing quality/yields; and impairments of longlived assets, including manufacturing, assembly/test and intangible assets. The majority of Intel's non-marketable equity investment portfolio balance is concentrated in companies in the flash memory market segment, and declines in this market segment or changes in management's plans with respect to Intel's investments in this market segment could result in significant impairment charges, impacting restructuring charges as well as gains/losses on equity investments and interest and other. Intel's results could be affected by adverse economic, social, political and physical/infrastructure conditions in countries where Intel, its customers or its suppliers operate, including military conflict and other security risks, natural disasters, infrastructure disruptions, health concerns and fluctuations in currency exchange rates. Expenses, particularly certain marketing and compensation expenses, as well as restructuring and asset impairment charges, vary depending on the level of demand for Intel's products and the level of revenue and profits. Intel's results could be affected by the timing of closing of acquisitions and divestitures. Intel's results could be affected by adverse effects associated with product defects and errata (deviations from published specifications), and by litigation or regulatory matters involving intellectual property, stockholder, consumer, antitrust, disclosure and other issues, such as the litigation and regulatory matters described in Intel's SEC reports. An unfavorable ruling could include monetary damages or an injunction prohibiting Intel from manufacturing or selling one or more products, precluding particular business practices, impacting Intel's ability to design its products, or requiring other remedies such as compulsory licensing of intellectual property. A detailed discussion of these and other factors that could affect Intel's results is included in Intel's SEC filings, including the company's most recent Form 10-Q, Form 10-K and earnings release.

Rev. 5/4/12