# ECE 715 System on Chip Design and Test

# Lecture 20

INDRAPRASTHA INSTITUTE of INFORMATION TECHNOLOGY DELHI

# System on Chip Design and Test ECE 715

# **Power Dissipation in CMOS Circuits**

Lecture By Sidhartha Sankar Rout & Vinod Kumar Singh

INDRAPRASTHA INSTITUTE of INFORMATION TECHNOLOGY DELHI

# Why should we study about Power Dissipation?

#### Why should we study about Power Dissipation?

- Degradation of Performance

- Reliability Issue

Why Power issue has become an important concern in the present day VLSI circuit realization?

- Higher speed of operation

- Greater device leakage currents

- Increasing transistor count

## Where Does Power Go in CMOS?

- Dynamic

- Charging & Discharging of Capacitors

- Short-circuit

- Static

- Leakage

$$P_{total} = P_{dyn} + P_{stat}$$

$$P_{tran} + P_{sc} + P_{stat}$$

## **Dynamic Power Consumption**

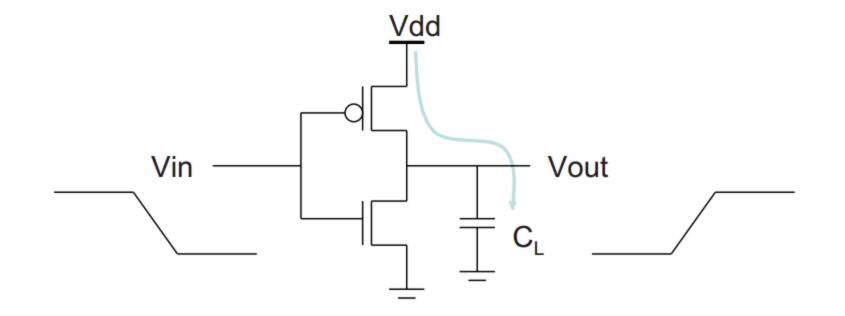

# Dynamic Capacitive Power and Energy stored in the PMOS Device

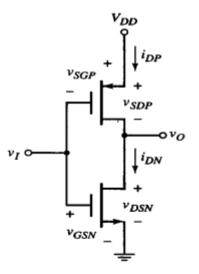

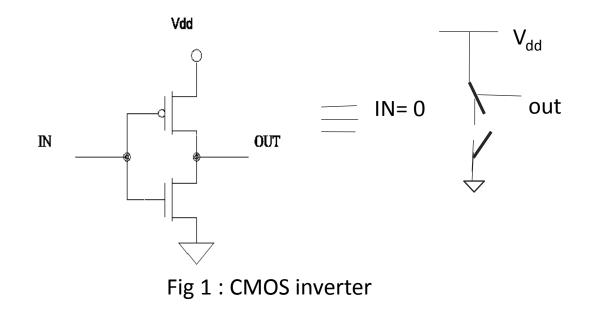

#### Case I: When the input is at logic 0

PMOS is conducting and NMOS is in cutoff mode The load capacitor must be charged through the PMOS device. Power dissipation in the PMOS transistor is given by:

$\mathsf{P}_{\mathsf{P}} = \mathsf{i}_{\mathsf{L}} \mathsf{V}_{\mathsf{SD}} = \mathsf{i}_{\mathsf{L}} (\mathsf{V}_{\mathsf{DD}} \mathsf{-} \mathsf{V}_{\mathsf{O}})$

The current and output voltages are related by:

$i_L = C_L dv_O / dt$

Energy dissipation in the PMOS device as the output switches from low to high:

$$E_{P} = \int_{0}^{\infty} P_{P} dt = \int_{0}^{\infty} C_{L} (V_{DD} - v_{O}) \frac{dv_{O}}{dt} dt, E_{P} = C_{L} V_{DD} \int_{0}^{V_{DD}} dv_{O} - C_{L} \int_{0}^{V_{DD}} v_{O} dv_{O} dv$$

Above equation showed the energy stored in the capacitor  $C_L$  when the output is high.

$V_{DD}$

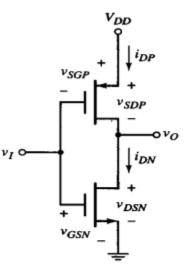

## Power Dissipation and Total Energy Stored in the CMOS Device

### Case II: when the input is high and out put is low:

During switching all the energy stored in the load capacitor is dissipated in the NMOS device.

The energy dissipated in the NMOS inverter can be written as,

$E_N = \frac{1}{2} C_L V_{DD}^2$

The total energy dissipated during one switching

$$E_T = E_P + E_N = \frac{1}{2} C_L V_{DD}^2 + \frac{1}{2} C_L V_{DD}^2 = C_L V_{DD}^2$$

The power dissipated

$$E_T = Pt \Rightarrow P = \frac{E_T}{t} \Rightarrow P = fE_T \Rightarrow fC_L V_{DD}^2$$

This implied that the power dissipation in the CMOS inverter is directly proportional to switching frequency and VDD<sup>2</sup>

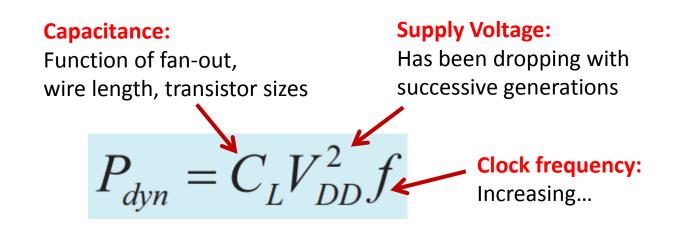

Formula for dynamic power:

$$P_{dyn} = C_L V_{DD}^2 f$$

Most gates do not operate / switch at every clock cycle, they are often accompanied by a factor  $\alpha$ , called the activity factor.

Now, the dynamic power dissipation may be rewritten as

$$P_{dyn} = \alpha C_L V_{DD}^2 f$$

Observations:

- Not a function of transistor sizes!

- A function of switching activity!

# Lowering Dynamic Power

#### **Dynamic Power Reduction Techniques:**

- Clock Gating

- □ Multy V<sub>DD</sub>

- DVFS (Dynamic Voltage & Frequency Scaling)

### **DVFS**

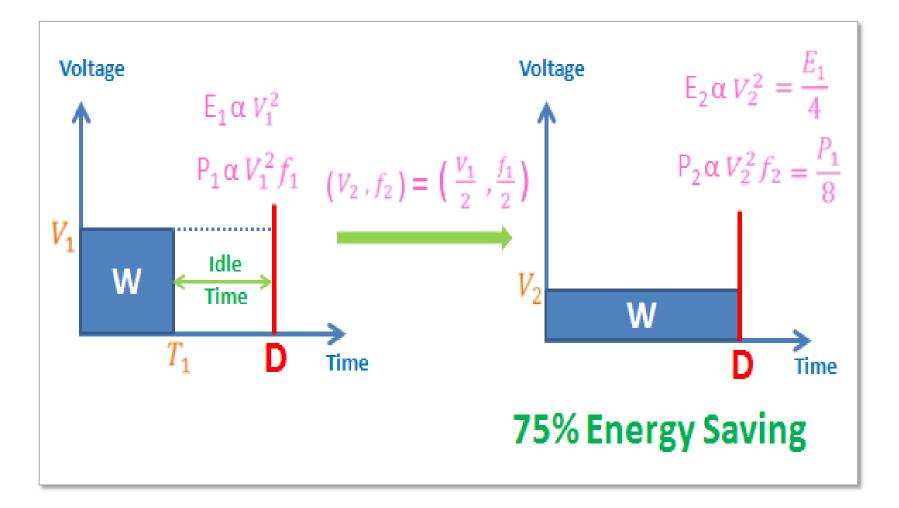

**DVFS** dynamically scales the operating frequency and supply voltage to provide just enough performance to process the application workload while meeting the compute time, and thereby, reducing the energy dissipation.

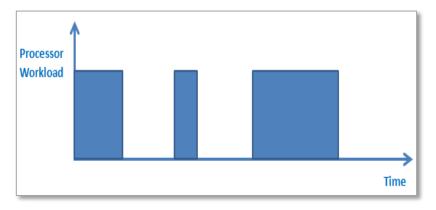

A typical workload pattern with tasks and idle time between tasks

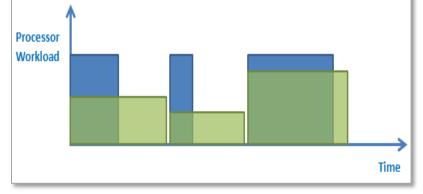

A typical workload pattern with DVFS technique

The DVFS technique can significantly improve the processor energy efficiency especially for portable systems which are battery or UPS powered electronic devices.

# Energy saving calculation in DVFS technique

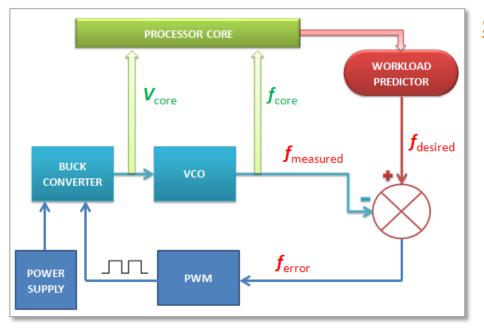

# Block diagram of DVFS Control Loop

#### Sequence of Operation of the Control Loop

1. Workload Predictor will decide the desired frequency in the next DVFS interval.

2. An Adder will generate an error frequency value from the predicted frequency of the next DVFS interval and the measured frequency of the current DVFS interval.

3. The value of error frequency will control the duty cycle of the modulated pulse generated at the output of the Pulse Width Modulator.

4. Buck Converter will take the input from the power supply and a controlled input as the PWM modulated signal. This generates the required voltage level for the processor.

5. The dc voltage generated by the Buck Converter will be the controlled voltage for the VCO and the required frequency level for the processor will be generated.

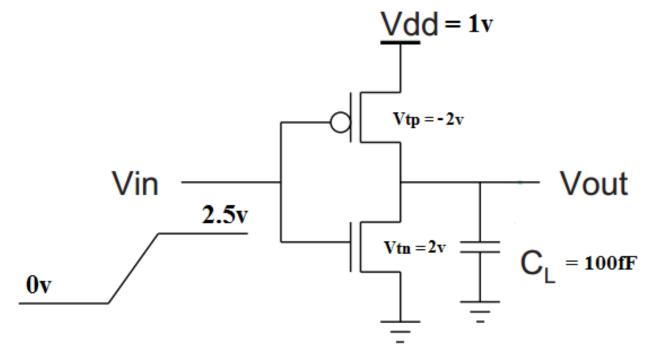

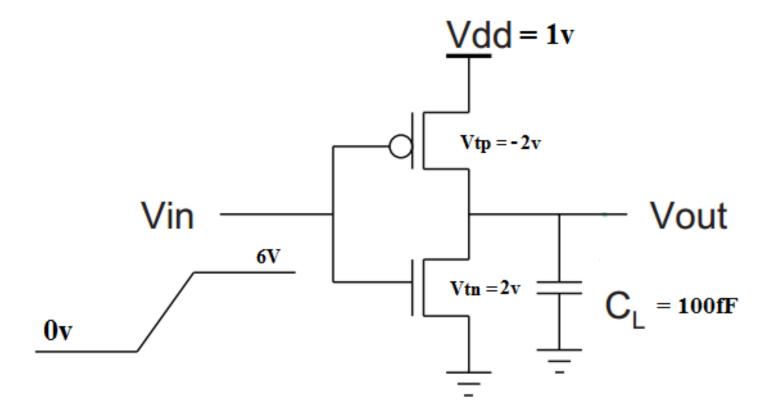

Find the Dynamic Power dissipation of the following CMOS inverter circuit.

The operating frequency of the circuit is 1GHz and consider the activity factor as  $\alpha = 1$

# Static Power in Submicron Rregion

• What does "Static" mean in CMOS VLSI Circuits?

- Active Mode While chip is doing useful work

- Standby Mode Chip is idle (clocks are stopped power due to switching is saved)

- Sleep Mode No supply to functionally inactive block in chip

# Static Power in Submicron Rregion

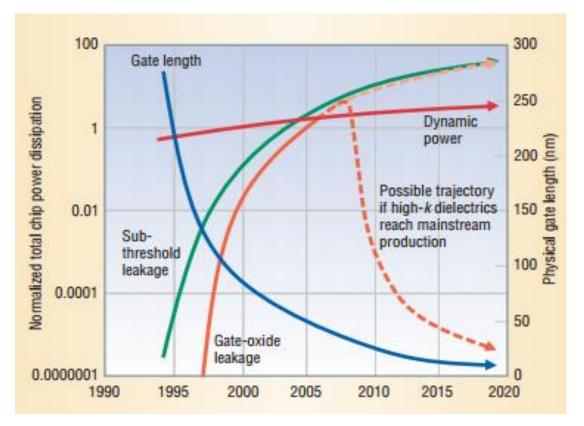

• Why is "Static Power" so significant in Deep Submicron Technology?

Fig 2 : Dynamic and Static power dissipation according to ITRS

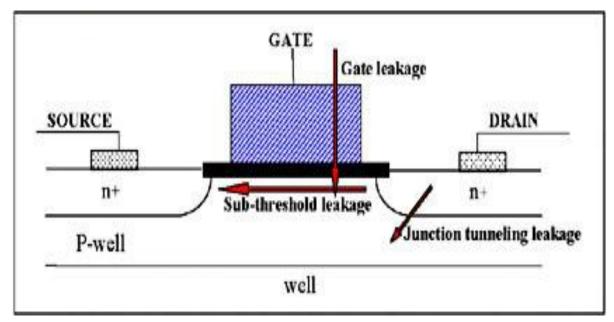

- Static power dissipation due to

- Sub-threshold leakage through OFF transistors

- Gate leakage through gate dielectric (gate to body)

- Junction leakage from source/drain diffusions to body or well

#### Fig 3 : Leakage Current in a Transistor

when transistors are nominally OFF, they leak small amounts of current from drain to source called sub-threshold

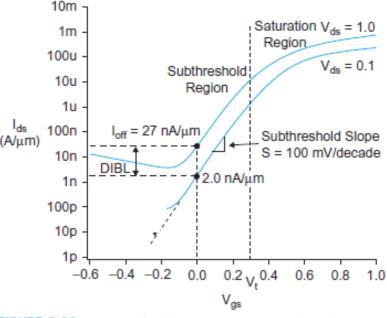

• For Vds > 50 mV (typical value of  $V_{th}$ )

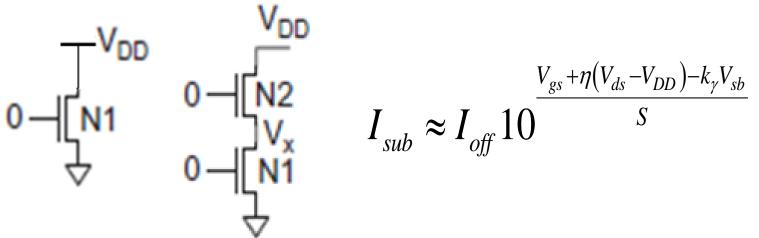

$$I_{sub} \approx I_{off} 10^{\frac{V_{gs} + \eta (V_{ds} - V_{DD}) - k_{\gamma} V_{sb}}{S}}$$

•

$$I_{off}$$

= leakage at  $V_{gs}$  = 0,  $V_{ds}$  =  $V_{DD}$

FIGURE 2.20 I-V characteristics of a 65 nm nMOS transistor at 70 °C on a log scale

$I_{off}$  is a key process parameter defining the leakage of a single OFF transistor range from 100nm/um at low V<sub>th</sub> to 1nm/um at high V<sub>th</sub>

$$k_{_{\gamma}}$$

is the body effect coefficient

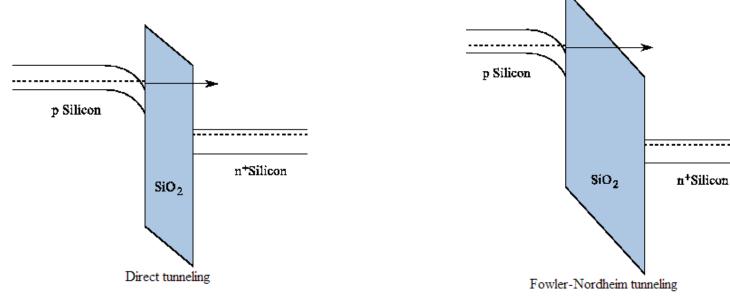

# Gate Leakage

- It is quantum-mechanical effect caused by tunneling through the extremely thin gate dielectric.

- Two physical mechanisms for gate tunneling are

- Direct tunneling Important at Low voltage and thin oxides (dominant leakage component)

- Fowler-Nordheim (FN) tunneling High voltage and Moderate thickness

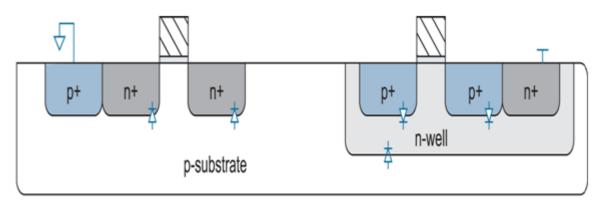

### Junction Leakage

- The p–n junctions between diffusion and the substrate or well form diodes

- Keep Well at high voltage and body at low voltage forms reverse biased junction hence leakage

#### Fig 4 : Reveres biased pn junction diodes in CMOS

# Leakage Reduction Technique

Fig 5 : Series off transistor for demonstrating stack effect

• If Vx is small, N1 will see a much smaller DIBL effect and will leak less

• As Vx rises, V<sub>as</sub> for N2 becomes negative, reducing its leakage

# Leakage Reduction Technique ..

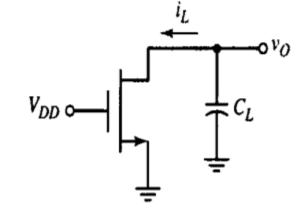

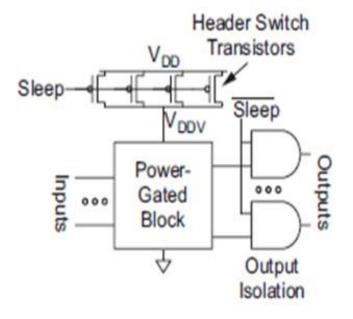

Power Gating

Reduction in static current during sleep mode is to turn off the power supply to the sleeping blocks this technique called **Power Gating**

Fig 6 : Power Gating

Note : Power gating introduces a number of design issues

Multiple  $V_{th}$

- + Low  $V_{th}$  \_\_ Used for high performance in critical circuit

- High Vth -- Used for rest of circuit (95%) for low leakage

$$V_{th} = V_{th0} + \gamma (\sqrt{\phi_s + V_{sb}} - \sqrt{\phi_s}) = V_{th} = V_{th0} + k_{\gamma} V_{sb}$$

Here  $\gamma = \frac{\sqrt{2q\varepsilon_{si}}N_A}{C_{ox}}$   $\phi_s = 2v_t \ln \frac{N_A}{n_i}$   $k_{\gamma} = \frac{\gamma}{2\sqrt{\phi_s}}$

Note : body bias can intentionally be applied to alter the threshold voltage, permitting trade-offs between performance and sub-threshold leakage current

Let both the transistors are in 65nm technology. Which is the major leakage current component for the NMOS over here.

Thank You