#### **Digital VLSI design**

# Lecture 10: Logical Effort

#

INDRAPRASTHA INSTITUTE of INFORMATION TECHNOLOGY DELHI

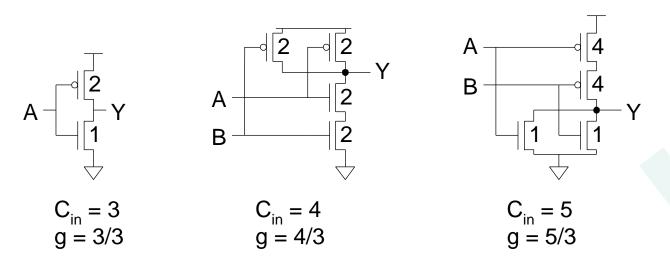

### **Computing Logical Effort**

- DEF: Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current.

- Measure from delay vs. fanout plots

- Or estimate by counting transistor widths

## Catalog of Gates

• Logical effort of common gates

| Gate type      | Number of inputs |      |          |              |          |  |

|----------------|------------------|------|----------|--------------|----------|--|

|                | 1                | 2    | 3        | 4            | n        |  |

| Inverter       | 1                |      |          |              |          |  |

| NAND           |                  | 4/3  | 5/3      | 6/3          | (n+2)/3  |  |

| NOR            |                  | 5/3  | 7/3      | 9/3          | (2n+1)/3 |  |

| Tristate / mux | 2                | 2    | 2        | 2            | 2        |  |

| XOR, XNOR      |                  | 4, 4 | 6, 12, 6 | 8, 16, 16, 8 |          |  |

## Catalog of Gates

- Parasitic delay of common gates

- In multiples of  $p_{inv}$  ( $\approx$ 1)

| Gate type      | Number of inputs |   |   |   |    |  |

|----------------|------------------|---|---|---|----|--|

|                | 1                | 2 | 3 | 4 | n  |  |

| Inverter       | 1                |   |   |   |    |  |

| NAND           |                  | 2 | 3 | 4 | n  |  |

| NOR            |                  | 2 | 3 | 4 | n  |  |

| Tristate / mux | 2                | 4 | 6 | 8 | 2n |  |

| XOR, XNOR      |                  | 4 | 6 | 8 |    |  |

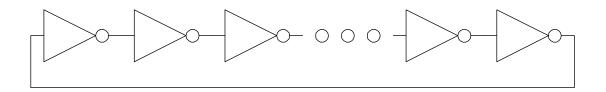

## **Example: Ring Oscillator**

• Estimate the frequency of an N-stage ring oscillator

Logical Effort: g =

- Electrical Effort: h =

- Parasitic Delay: p =

- Stage Delay: d =

Frequency: f<sub>osc</sub> =

5

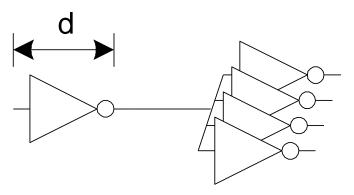

#### Example: FO4 Inverter

• Estimate the delay of a fanout-of-4 (FO4) inverter

- Logical Effort: g =

- Electrical Effort: h =

- Parasitic Delay: p =

- Stage Delay: d =

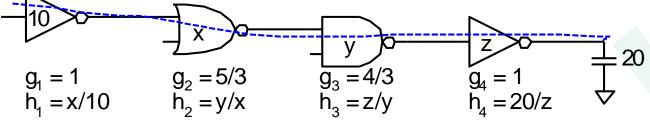

#### Multistage Logic Networks

- Logical effort generalizes to multistage networks

- Path Logical Effort

$$G = \prod g_i$$

Path Electrical Effort

$$H = \frac{C_{\text{out-path}}}{C_{\text{in-path}}}$$

$$F = \prod_{i=1}^{n} f_{i} - \prod_{i=1}^{n} f_{i}$$

• Path Effort

$$F = \prod f_i = \prod g_i h_i$$

#### Multistage Logic Networks

- Logical effort generalizes to multistage networks

- Path Logical Effort

$$G = \prod g_i$$

Path Electrical Effort

$$H = \frac{C_{out-path}}{C_{in-path}}$$

$$F = \prod f_i = \prod g_i h_i$$

- Path Effort

- Can we write F = GH?

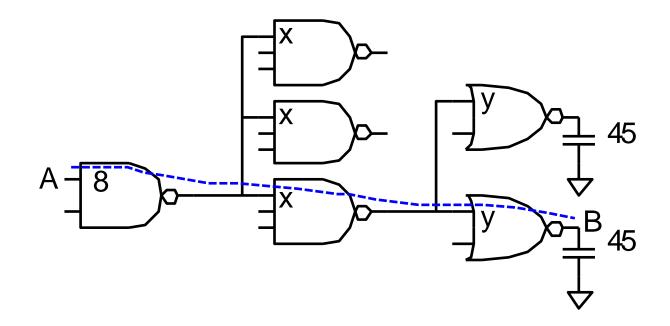

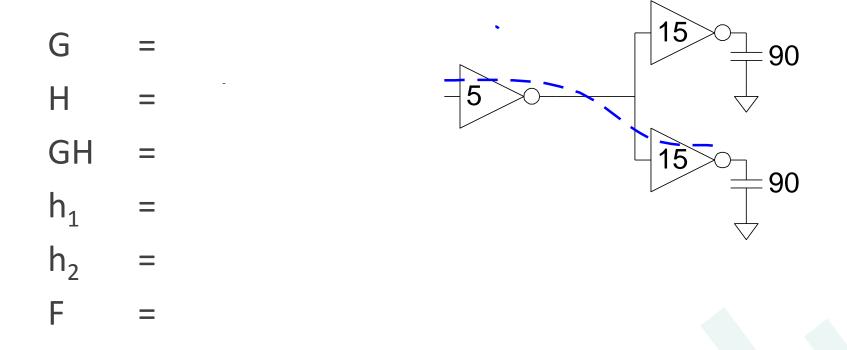

#### Paths that Branch

• No! Consider paths that branch:

## **Branching Effort**

- Introduce *branching effort*

- Accounts for branching between stages in path

$$b = \frac{C_{\text{on path}} + C_{\text{off path}}}{C_{\text{on path}}}$$

$$B = \prod b_i$$

Note:

$$\prod h_i = BH$$

Now we compute the path effort

## Multistage Delays

• Path Effort Delay

$$D_F = \sum f_i$$

Path Parasitic Delay

$$P = \sum p_i$$

• Path Delay

$$D = \sum d_i = D_F + P$$

$$D = \sum d_i = D_F + P$$

• Delay is smallest when each stage bears same effort

$$\hat{f} = g_i h_i = F^{\frac{1}{N}}$$

• Thus minimum delay of N stage path is

- This is a key result of logical effort

- Find fastest possible delay

- Doesn't require calculating gate sizes

#### Gate Sizes

• How wide should the gates be for least delay?

$$\hat{f} = gh = g \frac{C_{out}}{C_{in}}$$

$$\Rightarrow C_{in_i} = \frac{g_i C_{out_i}}{\hat{f}}$$

- Working backward, apply capacitance transformation to find input capacitance of each gate given load it drives.

- Check work by verifying input cap spec is met.

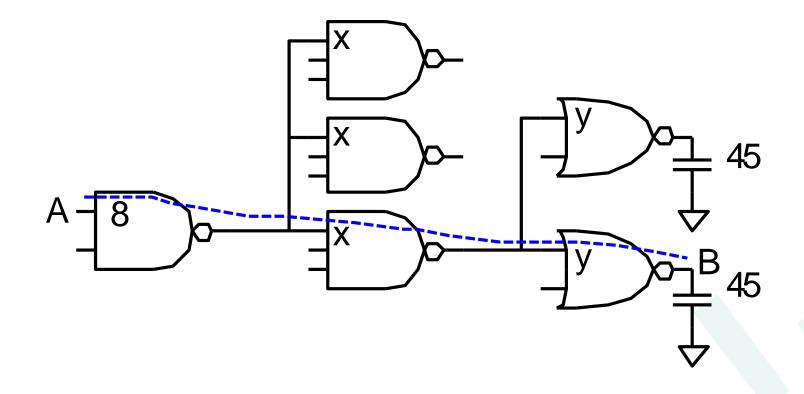

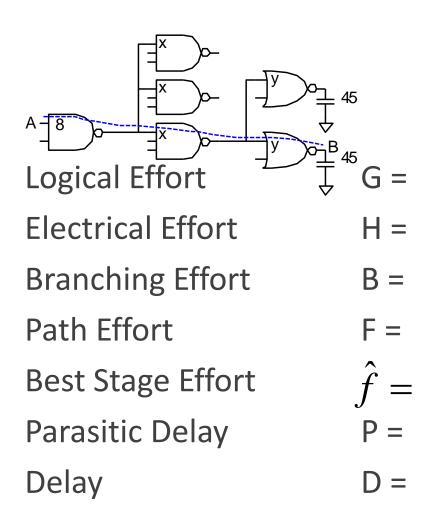

#### Example: 3-stage path

• Select gate sizes x and y for least delay from A to B

### Example: 3-stage path

# Example: 3-stage path

- Work backward for sizes

- y =

x =