### **Digital VLSI design**

# Lecture 13: Combinational Circuit Design

INDRAPRASTHA INSTITUTE of INFORMATION TECHNOLOGY DELHI

# HI- and LO-Skew

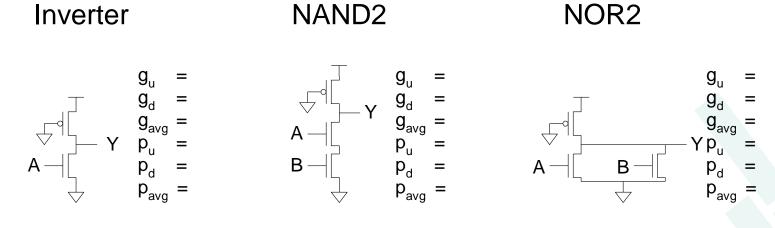

- Def: Logical effort of a skewed gate for a particular transition is the ratio of the input capacitance of that gate to the input capacitance of an unskewed inverter delivering the same output current for the same transition.

- Skewed gates reduce size of noncritical transistors

- HI-skew gates favor rising output (small nMOS)

- LO-skew gates favor falling output (small pMOS)

- Logical effort is smaller for favored direction

- But larger for the other direction

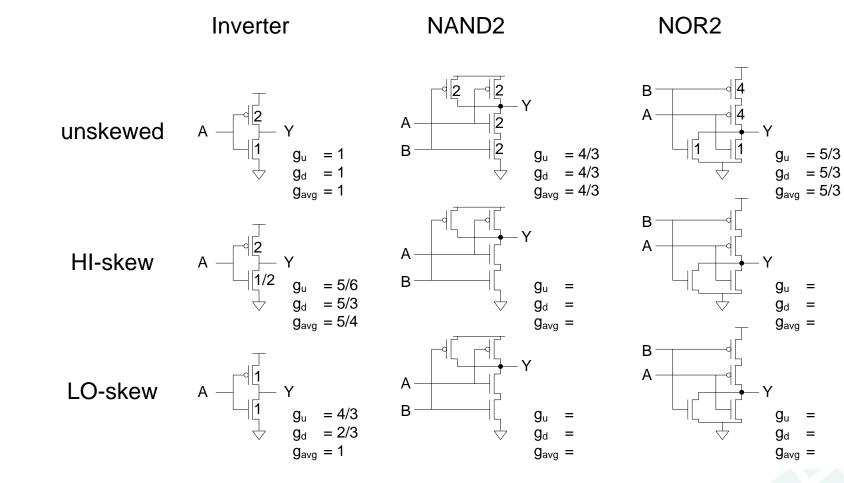

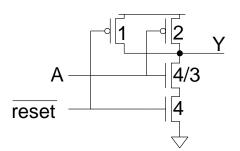

### Catalog of Skewed Gates

3

# Asymmetric Skew

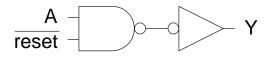

- Combine asymmetric and skewed gates

- Downsize noncritical transistor on unimportant input

- Reduces parasitic delay for critical input

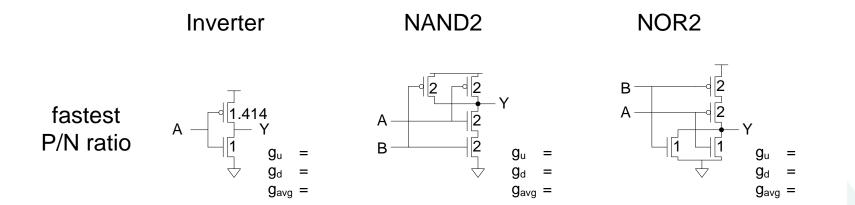

# Best P/N Ratio

- We have selected P/N ratio for unit rise and fall resistance ( $\mu$  = 2-3 for an inverter).

- Alternative: choose ratio for least average delay

- Ex: inverter

- Delay driving identical inverter

- t<sub>pdf</sub> =

- t<sub>pdr</sub> =

- t<sub>pd</sub> =

- $dt_{pd} / dP =$

- Least delay for P =

- In general, best P/N ratio is sqrt of equal delay ratio.

- Only improves average delay slightly for inverters

- But significantly decreases area and power

- For speed:

- NAND vs. NOR

- Many simple stages vs. fewer high fan-in stages

- Latest-arriving input

- For area and power:

- Many simple stages vs. fewer high fan-in stages

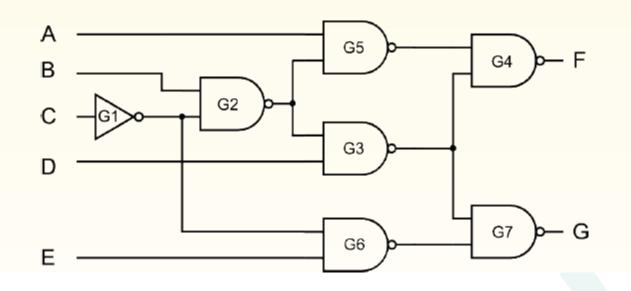

# **Another Example**

Size the path G1-G2-G3-G4 in the circuit below using logical effort Find the minimum delay and give the sizes of the P and N transistors to achieve this delay Assume that the off-path capacitance is the same as the on-path capacitance for each branch Input capacitance of Inverter G1 = 3 units. Load capacitance driven by Gate G4 = 52 units.

# **Circuit Families**

#

INDRAPRASTHA INSTITUTE of INFORMATION TECHNOLOGY **DELHI**

# Outline

- Pseudo-nMOS Logic

- Dynamic Logic

- Pass Transistor Logic

### Introduction

- What makes a circuit fast?

- I = C dV/dt  $\rightarrow$  t<sub>pd</sub>  $\propto$  (C/I)  $\Delta$ V

- low capacitance

- high current

- small swing

- Logical effort is proportional to C/I

- pMOS are the enemy!

- High capacitance for a given current

- Can we take the pMOS capacitance off the input?

- Various circuit families try to do this...

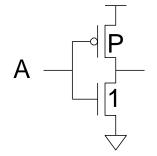

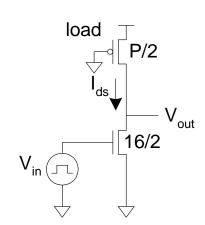

### Pseudo-nMOS

- In the old days, nMOS processes had no pMOS

- Instead, use pull-up transistor that is always ON

- In CMOS, use a pMOS that is always ON

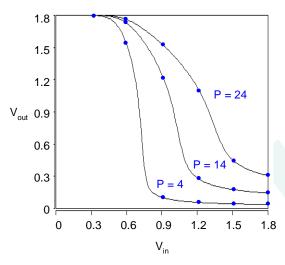

- Ratio issue

- Make pMOS about ¼ effective strength of pulldown network

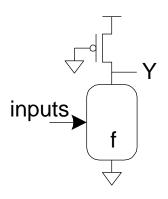

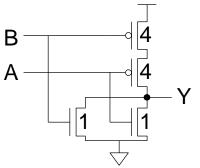

### Pseudo-nMOS Gates

- Design for unit current on output to compare with unit inverter.

- pMOS fights nMOS