#### **Digital VLSI design**

### Lecture 14: Circuit Families

###

INDRAPRASTHA INSTITUTE of INFORMATION TECHNOLOGY DELHI

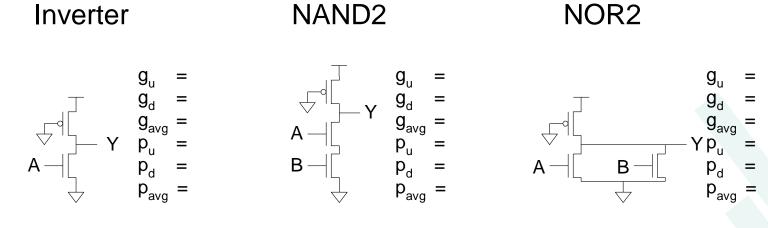

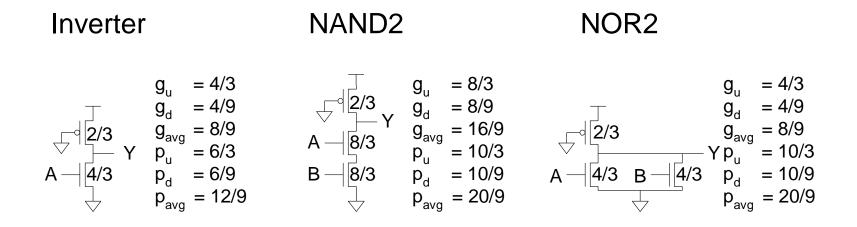

#### Pseudo-nMOS Gates

- Design for unit current on output to compare with unit inverter.

- pMOS fights nMOS

## Pseudo-nMOS Gates

- Design for unit current on output to compare with unit inverter.

- pMOS fights nMOS

### Pseudo-nMOS Design

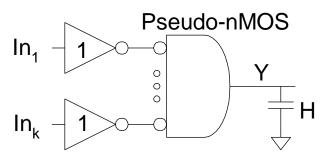

• Ex: Design a k-input AND gate using pseudo-nMOS. Estimate the delay driving a fanout of H

- F = G

- P = 1

- N = 2

- D = N

### Pseudo-nMOS Power

- Pseudo-nMOS draws power whenever Y = 0

- Called static power  $P = I_{DD}V_{DD}$

- A few mA / gate \* 1M gates would be a problem

- Explains why Pseudo-nMOS went extinct

- Use pseudo-nMOS sparingly for wide NORs

- Turn off pMOS when not in use

- The chip contains a 32 word x 48 bit ROM

- Uses pseudo-nMOS decoder and bitline pullups

- On average, one wordline and 24 bitlines are high

- Find static power drawn by the ROM

•

$$I_{on-p} = 36 \ \mu A$$

,  $V_{DD} = 1.0 \ V$

• Solution:

$$P_{\text{pull-up}} =$$

$P_{\text{static}} =$

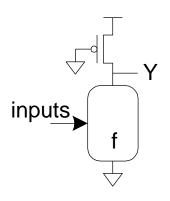

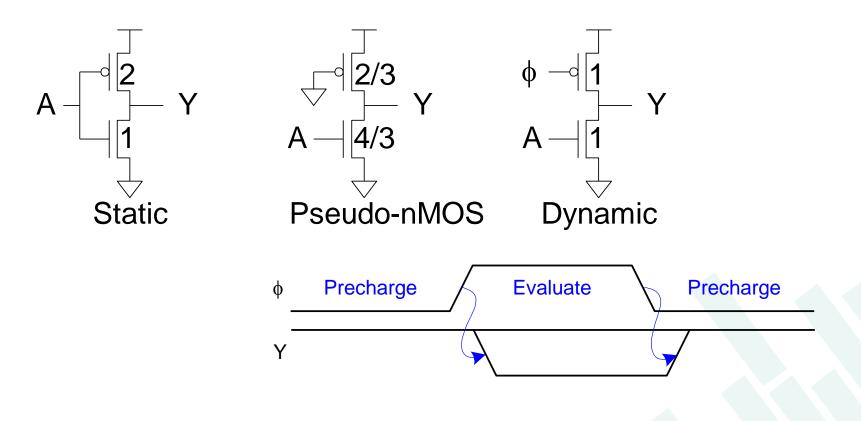

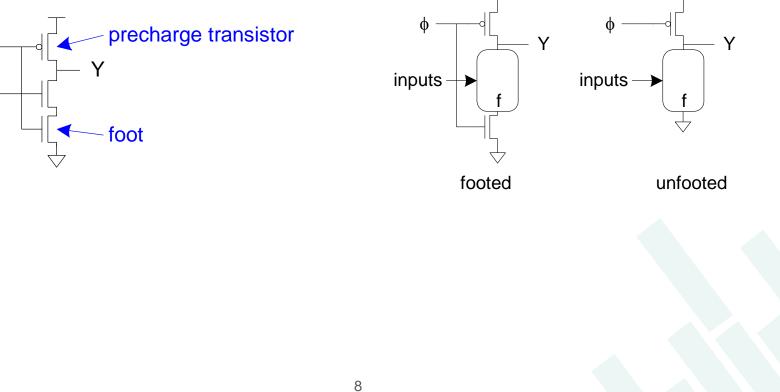

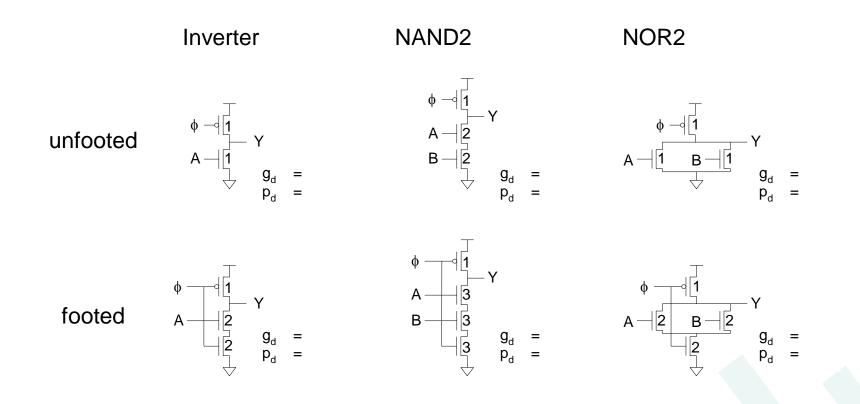

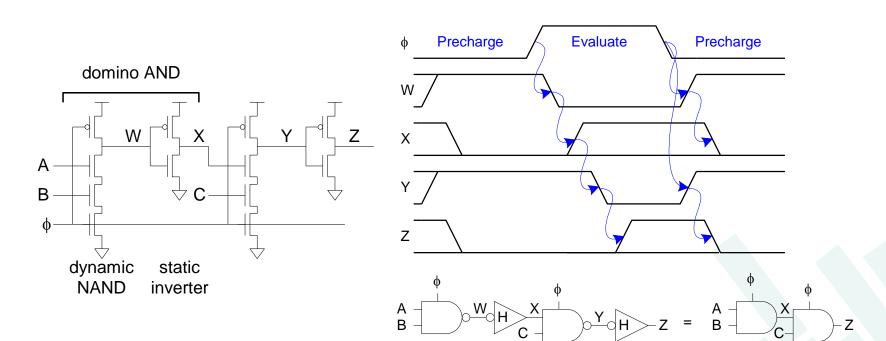

### Dynamic Logic

- *Dynamic* gates uses a clocked pMOS pullup

- Two modes: *precharge* and *evaluate*

• What if pulldown network is ON during precharge?

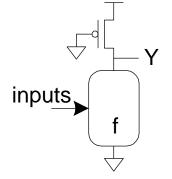

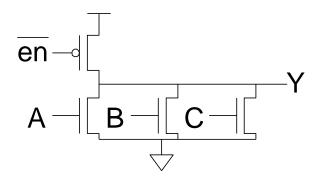

#### The Foot

0

А

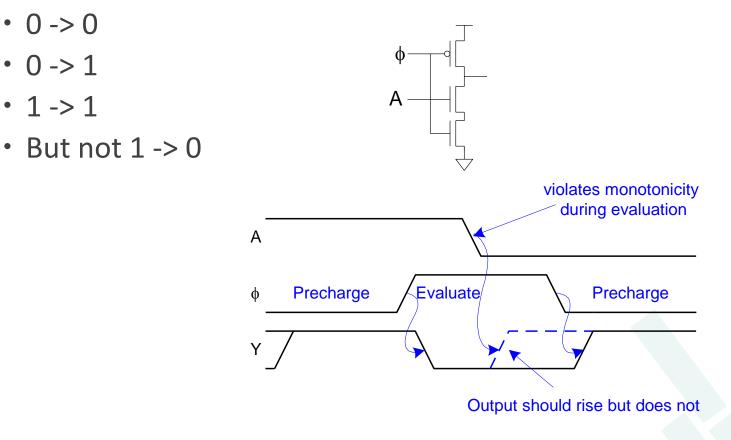

#### Monotonicity

• 0 -> 0

• 0 -> 1

• 1 -> 1

• Dynamic gates require *monotonically rising* inputs during evaluation

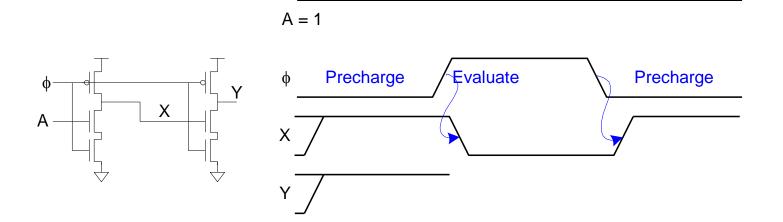

# Monotonicity Woes

- But dynamic gates produce monotonically falling outputs during evaluation

- Illegal for one dynamic gate to drive another!

### Produces monotonic outputs

Follow dynamic stage with inverting static gate

• Dynamic / static pair is called domino gate

### Domino Gates