#### **Digital VLSI design**

## Lecture 18: Scaling

##

INDRAPRASTHA INSTITUTE of INFORMATION TECHNOLOGY DELHI

#### Mid Sem Performance

- ECE 314:

- Average: 53.21 (out of 100)

- Highest: 85

- Lowest: 09

- ECE 514:

- Average: 79.87 (out of 125)

- Highest: 115

- Lowest: 58

### Outline

- Scaling

- Transistors

- Interconnect

- Future Challenges

- Economics

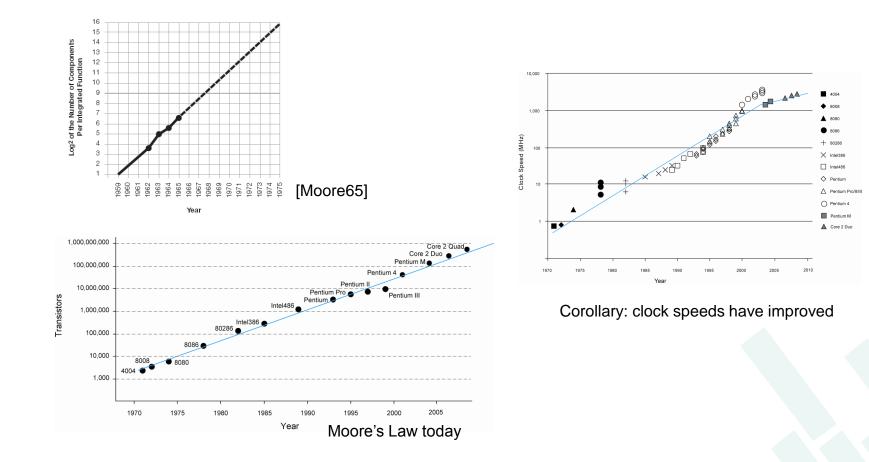

#### Moore's Law

Recall that Moore's Law has been driving CMOS

## Why?

- Why more transistors per IC?

- Smaller transistors

- Larger dice

- Why faster computers?

- Smaller, faster transistors

- Better microarchitecture (more IPC)

- Fewer gate delays per cycle

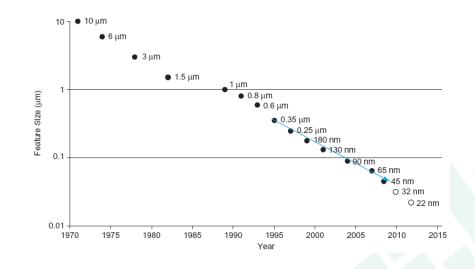

## Scaling

- The only constant in VLSI is constant change

- Feature size shrinks by 30% every 2-3 years

- Transistors become cheaper

- Transistors become faster and lower power

- Wires do not improve (and may get worse)

- Scale factor S

- Typically  $S = \sqrt{2}$

- Technology nodes

## **Dennard Scaling**

- Proposed by Dennard in 1974

- Also known as constant field scaling

- Electric fields remain the same as features scale

- Scaling assumptions

- All dimensions (x, y, z => W, L, t<sub>ox</sub>)

- Voltage (V<sub>DD</sub>)

- Doping levels

# **Device Scaling**

| Parameter                              | Sensitivity                      | Dennard Scaling  |

|----------------------------------------|----------------------------------|------------------|

| L: Length                              |                                  | 1/S              |

| W: Width                               |                                  | 1/S              |

| t <sub>ox</sub> : gate oxide thickness |                                  | 1/S              |

| V <sub>DD</sub> : supply voltage       |                                  | 1/S              |

| V <sub>t</sub> : threshold voltage     |                                  | 1/S              |

| NA: substrate doping                   |                                  | S                |

| β                                      | W/(Lt <sub>ox</sub> )            | S                |

| I <sub>on</sub> : ON current           | $\beta(V_{DD}-V_t)^2$            | 1/S              |

| R: effective resistance                | V <sub>DD</sub> /I <sub>on</sub> | 1                |

| C: gate capacitance                    | WL/t <sub>ox</sub>               | 1/S              |

| τ: gate delay                          | RC                               | 1/S              |

| f: clock frequency                     | 1/τ                              | S                |

| E: switching energy / gate             | CV <sub>DD</sub> <sup>2</sup>    | 1/S <sup>3</sup> |

| P: switching power / gate              | Ef                               | 1/S <sup>2</sup> |

| A: area per gate                       | WL                               | 1/S <sup>2</sup> |

| Switching power density                | P/A                              | 1                |

| Switching current density              | I <sub>on</sub> /A               | S                |

- Gates get faster with scaling (good)

- Dynamic power goes down with scaling (good)

- Current density goes up with scaling (bad)

#### Example

- Gate capacitance is typically about 1 fF/ $\mu$ m

- The typical FO4 inverter delay for a process of feature size f (in nm) is about 0.5f ps

- Estimate the ON resistance of a unit (4/2  $\lambda$ ) transistor.

# **Real Scaling**

- $t_{ox}$  scaling has slowed since 65 nm

- Limited by gate tunneling current

- Gates are only about 4 atomic layers thick!

- High-k dielectrics have helped continued scaling of effective oxide thickness

- $V_{DD}$  scaling has slowed since 65 nm

- SRAM cell stability at low voltage is challenging

- Dennard scaling predicts cost, speed, power all improve

- Below 65 nm, some designers find they must choose just two of the three

### Wire Scaling

- Wire cross-section

- w, s, t all scale

- Wire length

- Local / scaled interconnect

- Global interconnect

- Die size scaled by  $\rm D_{c}\,{\approx}\,1.1$

# **Interconnect Scaling**

| Parameter                                                  | Sensitivity                            | Scale Factor          |

|------------------------------------------------------------|----------------------------------------|-----------------------|

| w: width                                                   |                                        | 1/S                   |

| s: spacing                                                 |                                        | 1/S                   |

| t: thickness                                               |                                        | 1/S                   |

| h: height                                                  |                                        | 1/S                   |

| D <sub>c</sub> : die size                                  |                                        | D <sub>c</sub>        |

| R <sub>w</sub> : wire resistance/unit length               | 1/wt                                   | <b>S</b> <sup>2</sup> |

| C <sub>wf</sub> : fringing capacitance / unit length       | t/s                                    | 1                     |

| C <sub>wp</sub> : parallel plate capacitance / unit length | w/h                                    | 1                     |

| C <sub>w</sub> : total wire capacitance / unit length      | $C_{wf} + C_{wp}$                      | 1                     |

| t <sub>wu</sub> : unrepeated RC delay / unit length        | R <sub>w</sub> C <sub>w</sub>          | <b>S</b> <sup>2</sup> |

| twr: repeated RC delay / unit length                       | sqrt(RCR <sub>w</sub> C <sub>w</sub> ) | sqrt(S)               |

| Crosstalk noise                                            | w/h                                    | 1                     |

| E <sub>w</sub> : energy per bit / unit length              | $C_w V_{DD}^2$                         | 1/S <sup>2</sup>      |

# **Interconnect Delay**

| Parameter                | Sensitivity                    | Local / Semiglobal | Global                                     |

|--------------------------|--------------------------------|--------------------|--------------------------------------------|

| I: length                |                                | 1/S                | D <sub>c</sub>                             |

| Unrepeated wire RC delay | l <sup>2</sup> t <sub>wu</sub> | 1                  | S <sup>2</sup> D <sub>c</sub> <sup>2</sup> |

| Repeated wire delay      | lt <sub>wr</sub>               | sqrt(1/S)          | D <sub>c</sub> sqrt(S)                     |

| Energy per bit           | IEw                            | 1/S <sup>3</sup>   | D <sup>c</sup> /S <sup>2</sup>             |

- Capacitance per micron is remaining constant

- About 0.2 fF/ $\mu$ m

- Roughly 1/5 of gate capacitance

- Local wires are getting faster

- Not quite tracking transistor improvement

- But not a major problem

- Global wires are getting slower

- No longer possible to cross chip in one cycle

A 32 bit off-chip bus operating at 1.5V and 1GHz clock rate is driving a capacitance of 3pF/bit. Each bit is estimated to have a toggling probability of 0.25 at each clock cycle. What is the power dissipation in operating the bus?