## Final Project Part-1: SHA256

**ECE-111 Advanced Digital Design Project**

**Vishal Karna**

**Winter 2022**

JACOBS SCHOOL OF ENGINEERING Electrical and Computer Engineering

### **Final Project Guidelines**

#### □ Final Project Includes:

- Part-1 : Develop SHA256 RTL model

- Part-2 : Develop bitcoin hashing RTL model using SHA256 hash function

- 2a : Serial Implementation

- 2b : Parallel Implementation

#### □ Testbench will be provided for both Part-1 and Part-2:

- Expected behavior of SHA256 and bitcoin model will be implemented in testbench

- If RTL model does not generate correct hash value, then testbench will generate failure message otherwise it will generate success messages.

- Students have to ensure RTL models developed work as per the expectations

## **Final Project Guidelines**

#### □ Final Project Submission :

- Due date is Mar 18<sup>th</sup>, 2022 by 11.59 PM (No further extension beyond this date)

- Project report submitted after Mar 18<sup>th</sup> will not be accepted even for partial credit

- There is no presentation to be performed by each group on their final implementation

- Final report should include both SHA256 and Bitcoin model implementation results and details

- Note :

- Specifics details on what should final project submission include will be provided to students

- Specific files along with project report will be required to be submitted along with report.

O List of all files will be provided to students

- Project goals such as speed, area, timing, etc will be provided to students

#### **Project Discussion Sessions :**

- Teaching staff (TA's) will conduct project discussion sessions and office hours

- Students can reach out to TA' and Tutor to help with final project either in their office hours and/or through 1-1 zoom sessions. Students should request for such 1-1 session if required.

- Specific project discussion sessions conducted by instructor will be announced on piazza

3

## What is Secure Hash Algorithm (SHA256) ?

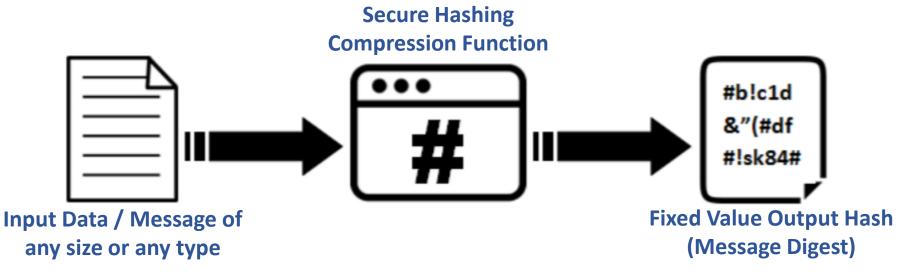

#### □ SHA stands for "Secure Hash Algorithm"

It is a cryptographic method of converting input data of any kind and size, into a string of fixed number of characters

- **Goal is to compute a unique hash value for any input data or message**

- □ No matter the size of the input, the output is the fixed size message digest

#### □ There are multiple SHA Algorithms

- SHA-1 : Input message up to <2^64 bits produces 160-bit output hash value (a.k.a message digest)

- SHA-2 : Input message up to 2^64 bits produces 256-bit output hash value

- SHA-3 : Input message of 2^128 bits produces 512-bit output hash value

### What is Secure Hash Algorithm (SHA256)?

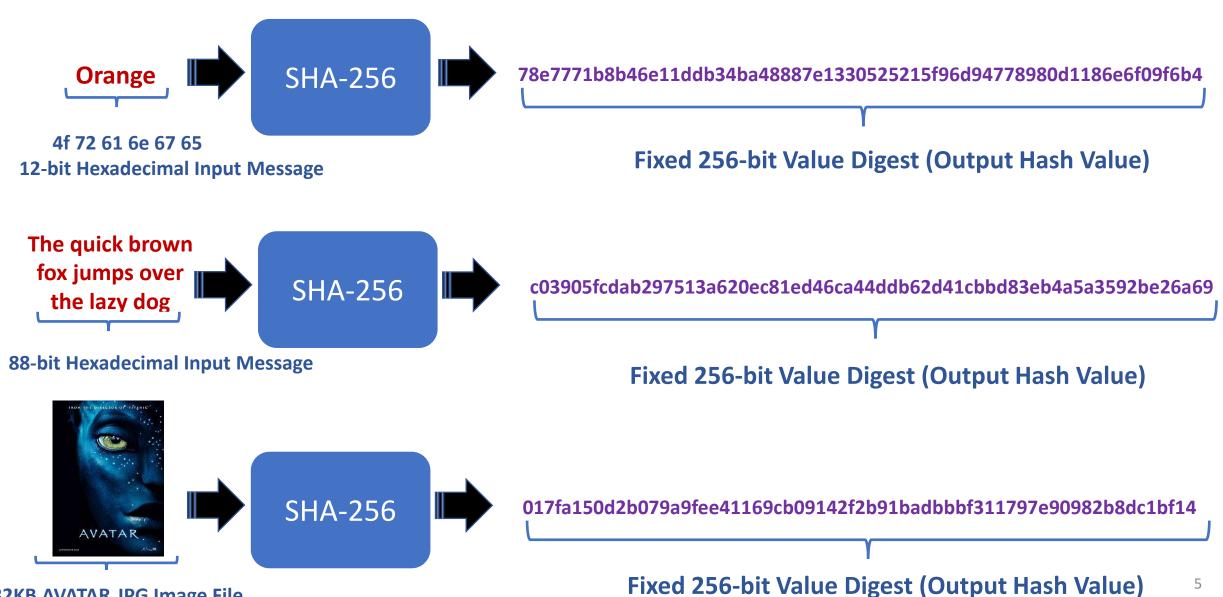

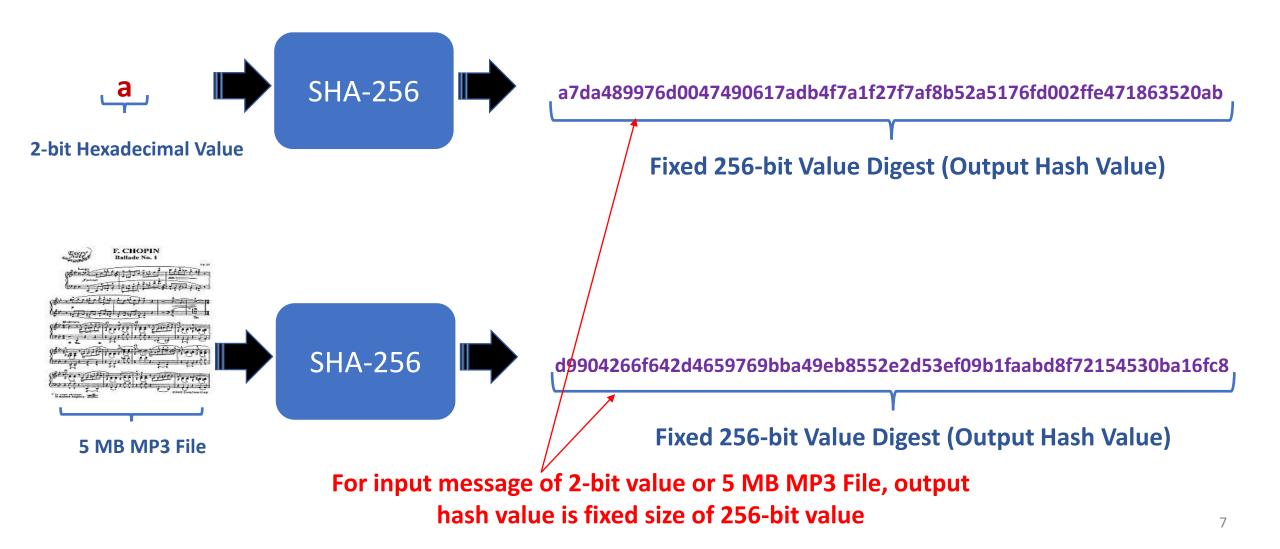

In SHA-256 messages up to 2^64 bits (2.3 billion gigabytes) are transformed into 256-bit digest

32KB AVATAR.JPG Image File

#### **SHA256** Properties

- Cryptographic hashing function needs to have certain properties in order to be completely secured. These are :

- Compression

- Avalanche Effect

- Determinism

- Pre-Image Resistant (One Way Function)

- Collision Resistance

- Efficient (Quick Computation)

#### Compression

Output hash should be a fixed number of characters, regardless of the size of the input message !

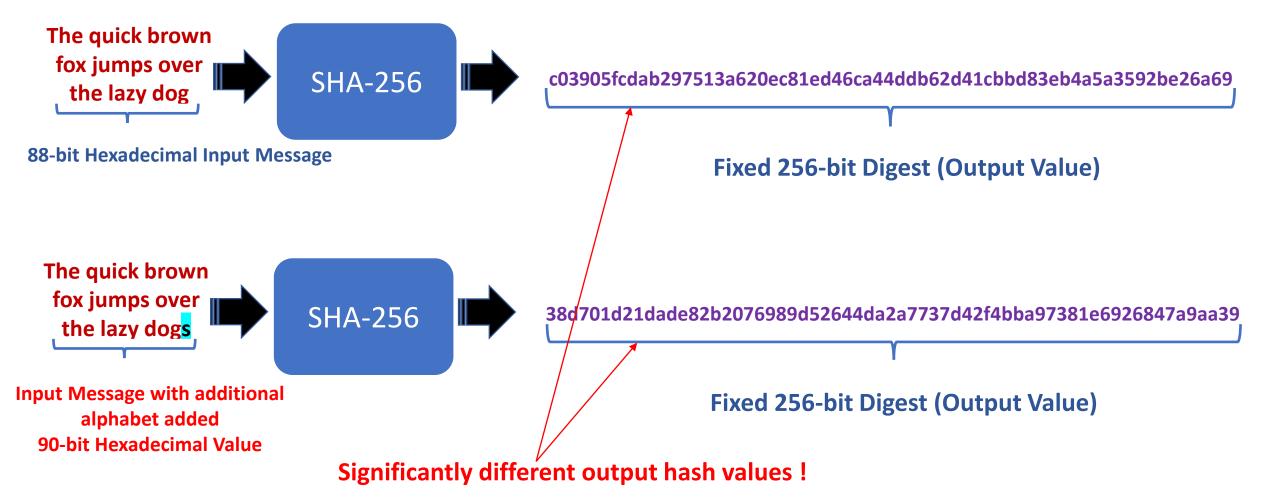

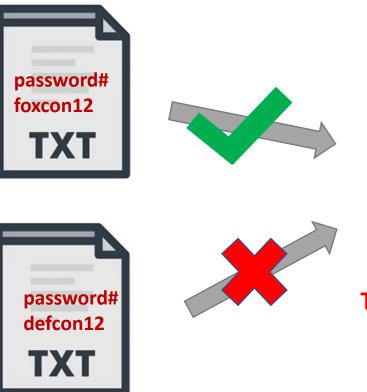

## **Avalanche Effect**

#### □ A minimal change in the input change the output hash value dramatically !

This is helpful to prevent hacker to predict output hash value by trial and error method

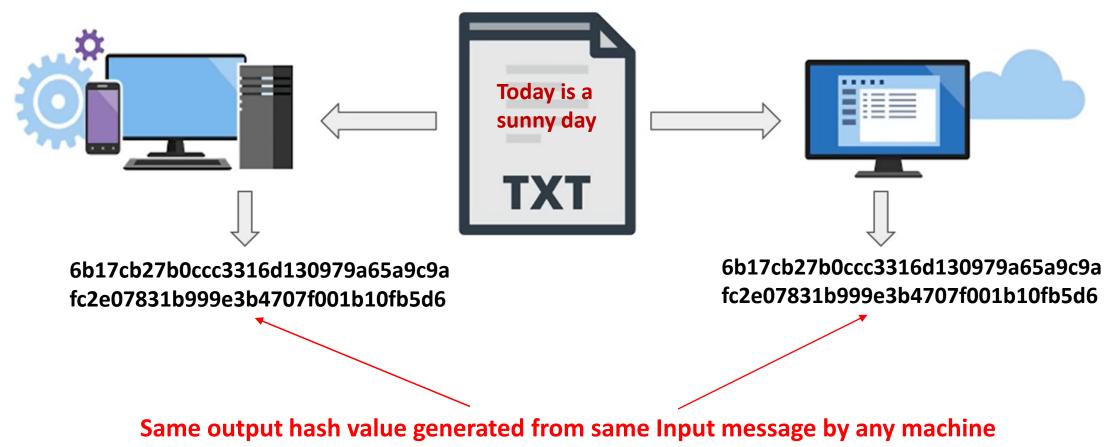

#### Determinism

#### □ Same input must always generate the same output by different systems

Any machine in the world which understands hashing algorithm should able generate same output hash value for a same input message

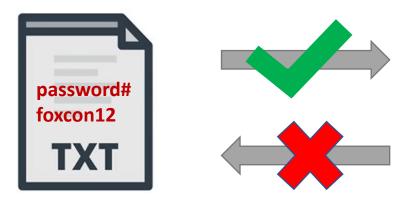

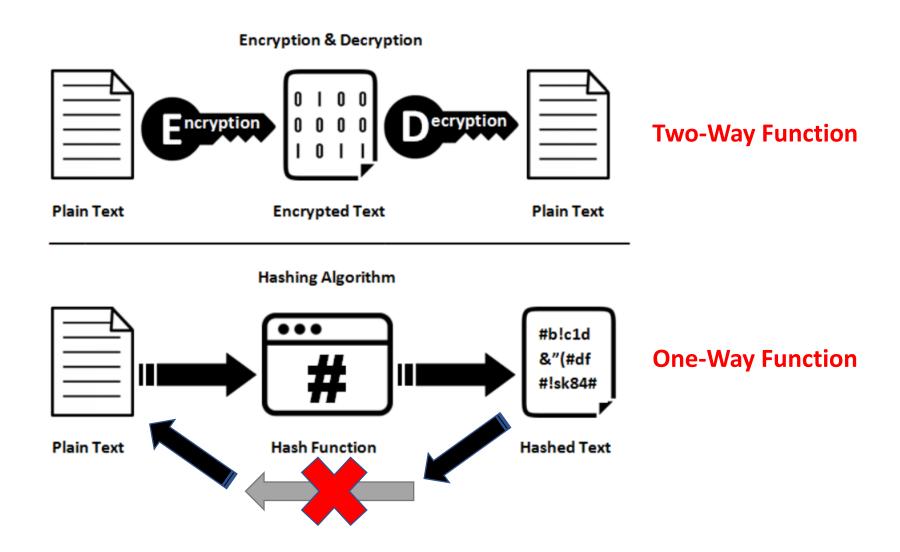

## **Pre-Image Resistant (One-Way) And Efficient**

#### □ Secure hashing algorithm should be a One-Way function

- No algorithm to reverse the hashing process to retrieve the original input message

- Only way is trial and error method, to try each possible input combination to find matching hash value. Not practical !

- If input message can be retrieved from output hash value then the whole concept will fail !

db2c26da2750dea1add7d7677c22d6dc b6dc4e2674357c82c39bb96d563f0578

Efficient : Creating the output hash should be a fast process that doesn't make heavy use of computing power

- Should not need supercomputers or high end machines to generate hash !

- More feasible for usage !

#### **Hashing vs Encryption**

Encryption is reversible as original message can be retrieved but Hashing has to be irreversible !

#### **Collision Resistance**

#### □ Hashing Function suffers from the same birthday problem

- What is a birthday problem !

- Two people can share same birthday as there are **365 days** in a year and there are **7.7+ billion** human beings on earth as of year 2020

$\circ$  **Tyron's** birthday is on June 1  $\rightarrow$  **152** (day of the year)

- $\circ$  Jenny's birthday is on December 31  $\rightarrow$  365 (day of the year)

- $\circ$  Sasha's birthday is on June 1  $\rightarrow$  152 (day of the year) shares Birthday hash 152 with Tyron

#### In rare occasions hashing may produce hash collision ! – Similar to Birthday Hash Problem

• Since input can be any large combination values and output is smaller fixed value, so it is theoretically possible to find two input messages having same output hash value

>f macroeconomic pessimism," said

t and chief economist, in a press

typically the most optimistic about

>ptimism around their personal financial

Two

different

inputs

the regular-season ends

possibility of seeing in hit

that he was approaching

#### Same Hash Value

DRT556677YYRGT63f05785230UGHTBKD 230UGHTBKGT53f15685EBVDF8901SWQ

## **Collision Resistance**

#### □ Hashing algorithm should be rigorous and it must withstand collision !

- Hackers may take advantage of hash collision

- To avoid hash collision, the output length of the hash value can be large enough so that birthday attack becomes computationally infeasible

- **Example :** Document hashed with SHA512 is more robust compared to SHA256 as possibility of two inputs to generate same long hash value is almost none !

Db2c26da2750dea1add7d7677c22d6dc b6dc4e2674357c82c39bb96d563f0578 78FGHWQ23409J5639bb96d77752190 8789VBDWTROPUTGHIKLMNOPTT891

Two different input blocks with same output hash value should be practically impossible even though theoretically possible !

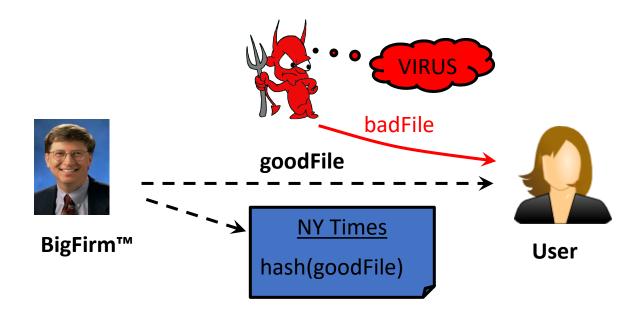

#### **Applications of SHA256 : Verifying File Integrity**

- Software manufacturer wants to ensure that the executable file is received by users without modification

- □ Sends out the file to users and publishes its hash in NY Times

- □ The goal is <u>integrity</u>, not secrecy

- Idea: given goodFile and hash(goodFile), very hard to find badFile such that hash(goodFile)=hash(badFile)

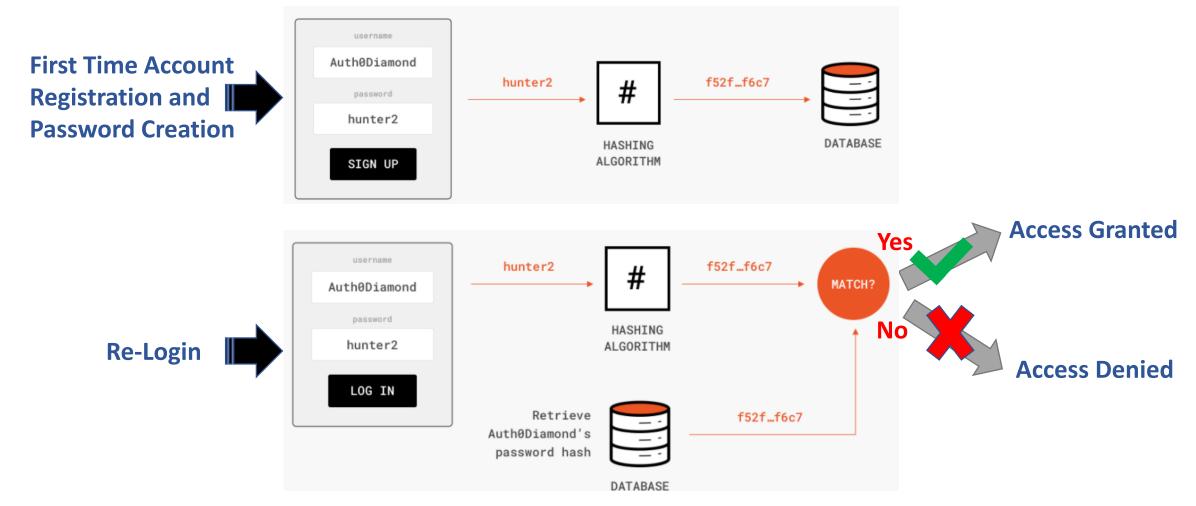

## **Applications of SHA256 : Storing and Validating Password**

Instead of storing password directly, password is stored in database as a hash value.

When user enters the password, first hash is created from the password and then hash value is checked against the originally stored hash value before granting the access

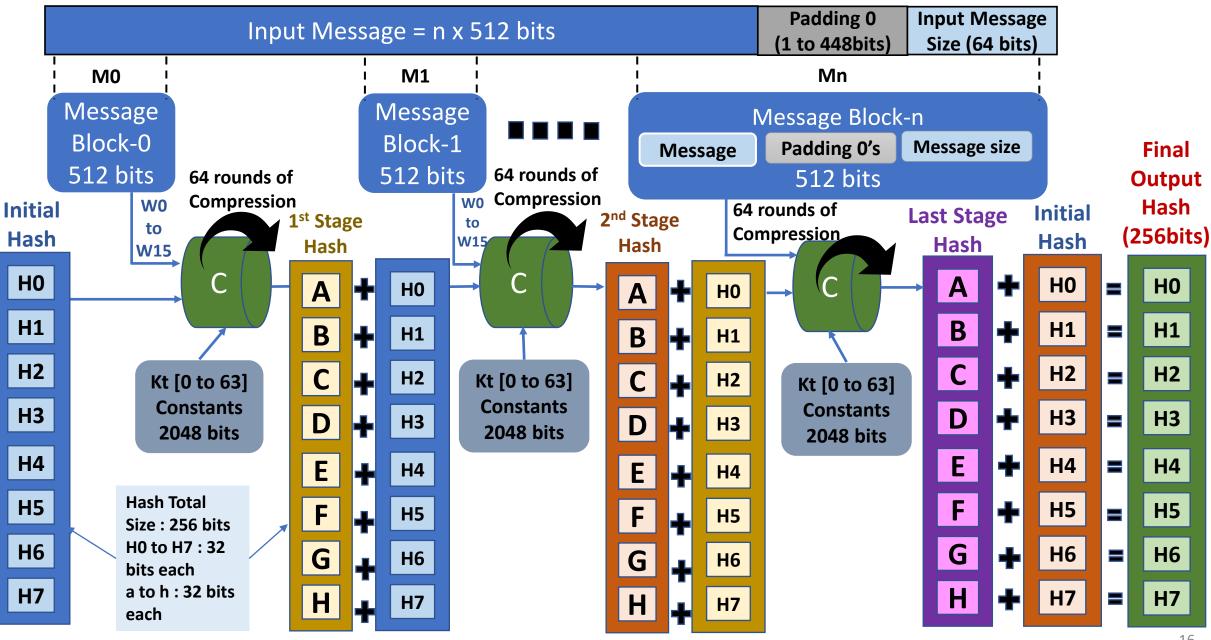

#### **General Assumptions**

- Input message must be <= 2<sup>64</sup> bits

- Message is processed in 512-bit blocks sequentially

- Message digest (output hash value) is 256 bits

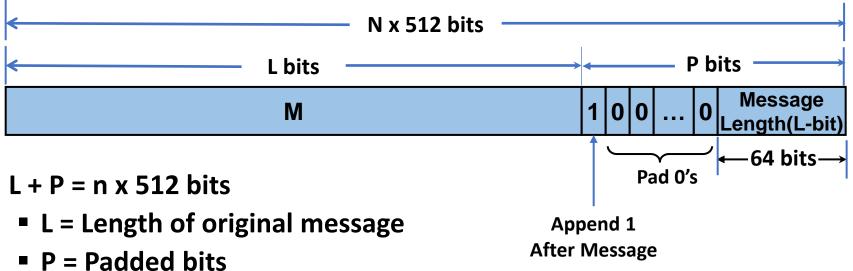

- □ Step 1: Append padding bits (1 and 0's)

- A L-bit message **M** is padded in the following manner:

- Add a single "1" to the end of M

- Then pad message with "O's" until the length of message is congruent to 448, modulo 512 (which means pad with O's until message is 64-bits less than some multiple of 512).

- □ Step 2 : Append message length bits in 0 to 63 bit position

- Since SHA256 supports until 2^64 input message size, 64 bits are required to append message length

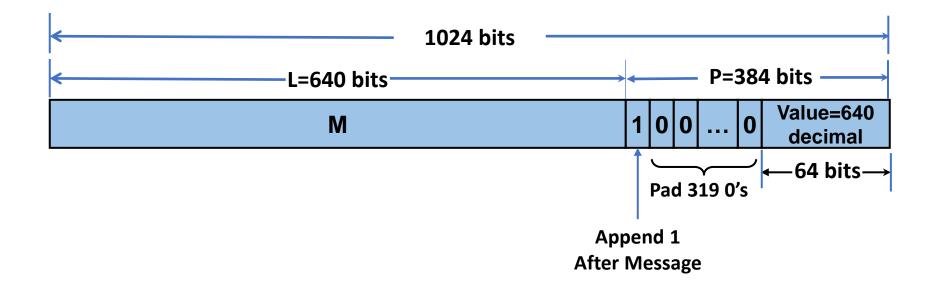

**Example :** Lets say, original Message is **L** = 640 bits

- Since message blocks have minimum 512 chunks, to fit original message of 640 bits in 512 bits chunks, it would require 2 message blocks (n = 2)

- **M0** (first block) Size = 512 bits (no padding required)

- M1 (second block) Size = 512 bits after padding

- $\circ$  **512 bits** = 128 bits of original message + 1 bit for appending '1' + 319 bits of 0's + 64 bit message length

- Message length=decimal value 640 stored in 0 to 63 bits

**Step 3 :** Buffer Initialization

Initialize message digest (MD) buffers / output hash to these 8 32-bit words

H0 = 6a09e667H1 = bb67ae85H2 = 3c6ef372H3 = a54ff53aH4 = 510e527fH5 = 9b05688cH6 = 1f83d9ab

H7 = 5be0cd19

**Step 4 :** Processing of the message (algorithm)

- Divide message M into 512-bit blocks, M<sub>0</sub>, M<sub>1</sub>, ... M<sub>i</sub>, ...

- Process each M<sub>i</sub> sequentially, one after the other

- Input:

- W<sub>t</sub>: a 32-bit word from the message

- K<sub>t</sub>: a constant array

- H0, H1, H2, H3, H4, H5, H6, H7 : current MD (Message Digest)

- Output:

- H0, H1, H2, H3, H4, H5, H6, H7 : new MD (Message Digest)

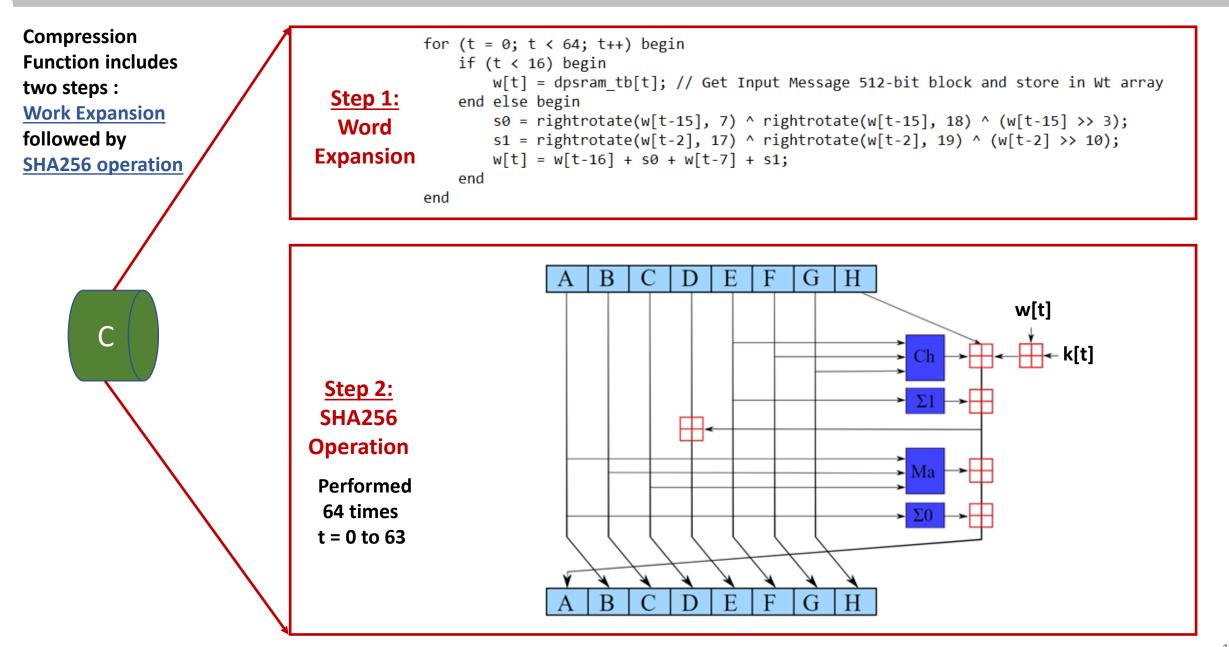

Step 4 : Cont'd

- At the beginning of processing each M<sub>j</sub>, initialize (A, B, C, D, E, F, G, H) = (H0, H1, H2, H3, H4, H5, H6, H7)

- Then 64 processing rounds of 512-bit blocks

- Each step t ( $0 \le t \le 63$ ): Word expansion for  $W_t$

- If t < 16

- $\circ$  W<sub>t</sub> = t<sup>th</sup> 32-bit word of block M<sub>j</sub>

- If  $16 \le t \le 63$

$\circ$  s<sub>0</sub> = (W<sub>t-15</sub> rightrotate 7) xor (W<sub>t-15</sub> rightrotate 18) xor (W<sub>t-15</sub> rightshift 3)  $\circ$  s<sub>1</sub> = (W<sub>t-2</sub> rightrotate 17) xor (W<sub>t-2</sub> rightrotate 19) xor (W<sub>t-2</sub> rightshift 10)  $\circ$  W<sub>t</sub> = W<sub>t-16</sub> + s<sub>0</sub> + W<sub>t-7</sub> + s<sub>1</sub>

#### □ Step 4: Cont'd

#### K<sub>t</sub> constants

K [0..63] = 0x428a2f98, 0x71374491, 0xb5c0fbcf, 0xe9b5dba5, 0x3956c25b, 0x59f111f1, 0x923f82a4, 0xab1c5ed5, 0xd807aa98, 0x12835b01, 0x243185be, 0x550c7dc3, 0x72be5d74, 0x80deb1fe, 0x9bdc06a7, 0xc19bf174, 0xe49b69c1, 0xefbe4786, 0x0fc19dc6, 0x240ca1cc, 0x2de92c6f, 0x4a7484aa, 0x5cb0a9dc, 0x76f988da, 0x983e5152, 0xa831c66d, 0xb00327c8, 0xbf597fc7, 0xc6e00bf3, 0xd5a79147, 0x06ca6351, 0x14292967, 0x27b70a85, 0x2e1b2138, 0x4d2c6dfc, 0x53380d13, 0x650a7354, 0x766a0abb, 0x81c2c92e, 0x92722c85, 0xa2bfe8a1, 0xa81a664b, 0xc24b8b70, 0xc76c51a3, 0xd192e819, 0xd6990624, 0xf40e3585, 0x106aa070, 0x19a4c116, 0x1e376c08, 0x2748774c, 0x34b0bcb5, 0x391c0cb3, 0x4ed8aa4a, 0x5b9cca4f, 0x682e6ff3, 0x748f82ee, 0x78a5636f, 0x84c87814, 0x8cc70208, 0x90befffa, 0xa4506ceb, 0xbef9a3f7, 0xc67178f2

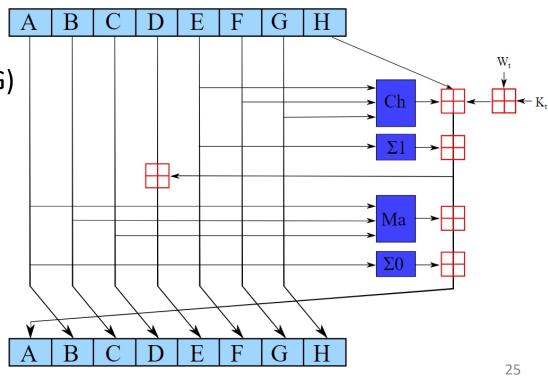

#### □ Step 4 : Cont'd

- Each step t ( $0 \le t \le 63$ ):

- **\Sigma O** S<sub>0</sub> = (A rightrotate 2) xor (A rightrotate 13) xor (A rightrotate 22)

- Ma maj = (A and B) xor (A and C) xor (B and C)

$t_2 = S_0 + maj$

- $S_1 = (E rightrotate 6) xor (E rightrotate 11) xor (E rightrotate 25)$

- Ch ch = (E and F) xor ((not E) and G)

$$t_1 = H + S_1 + ch + K[t] + W[t]$$

(A, B, C, D, E, F, G, H) =  $(t_1 + t_2, A, B, C, D + t_1, E, F, G)$

□ Step 4 : Cont'd

- Finally, when all 64 steps have been processed, set

- H0 = H0 + a

- H1 = H1 + b

- H2 = H2 + c

- H3 = H3 + d

- H4 = H4 + e

- H5 = H5 + f

- H6 = H6 + g

- H7 = H7 + h

**Step 5 :** Output

When all M<sub>j</sub> have been processed, the 256-bit hash of M is available in H0, H1, H2, H3, H4, H5, H6, H7

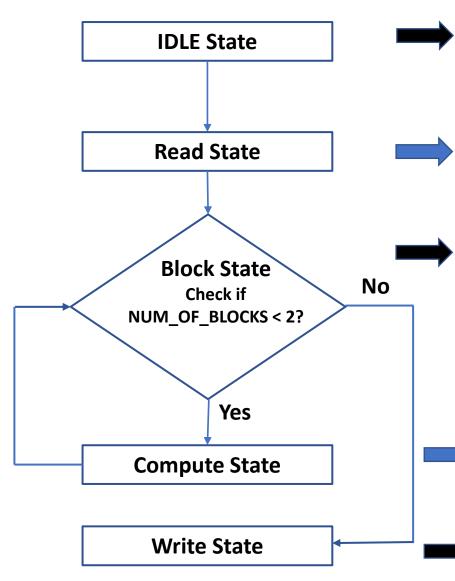

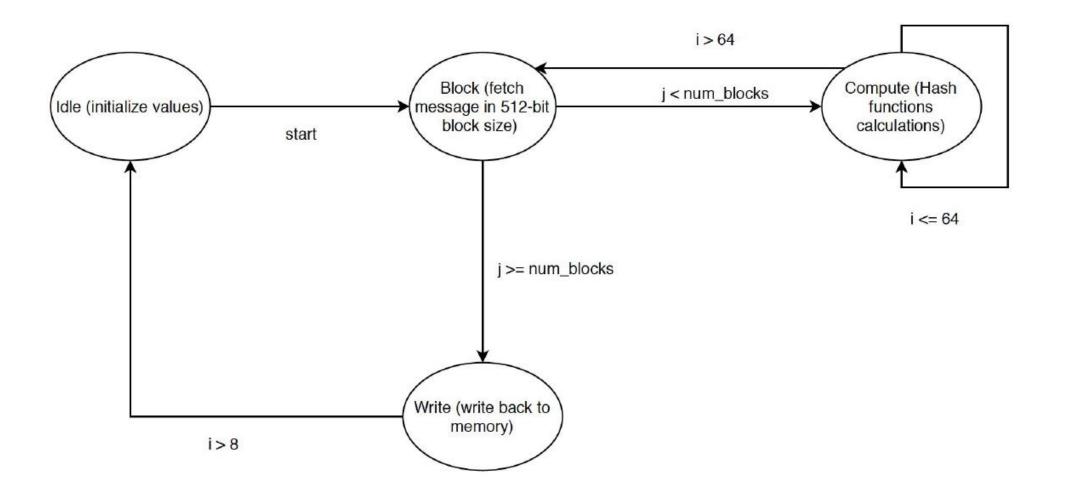

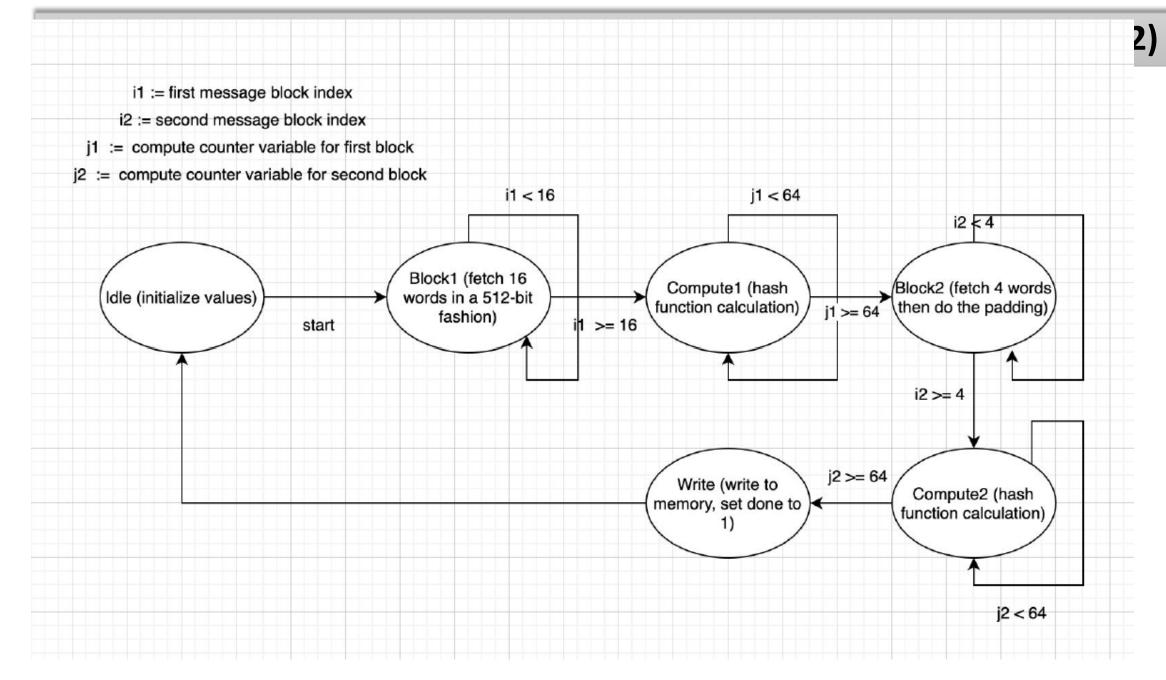

## SHA256 Algorithm Flow Chart for FSM Designing

- If start==1, Initialize h0, h1, h2, h3, h4, h5, h6, h7 to initial hash values

- Initialize a, b, c, d, e, f, g, h

- Initialize write enable to memory, memory address offset, curr\_addr to first message location in memory, index variables, etc

- Move to read input message FSM state

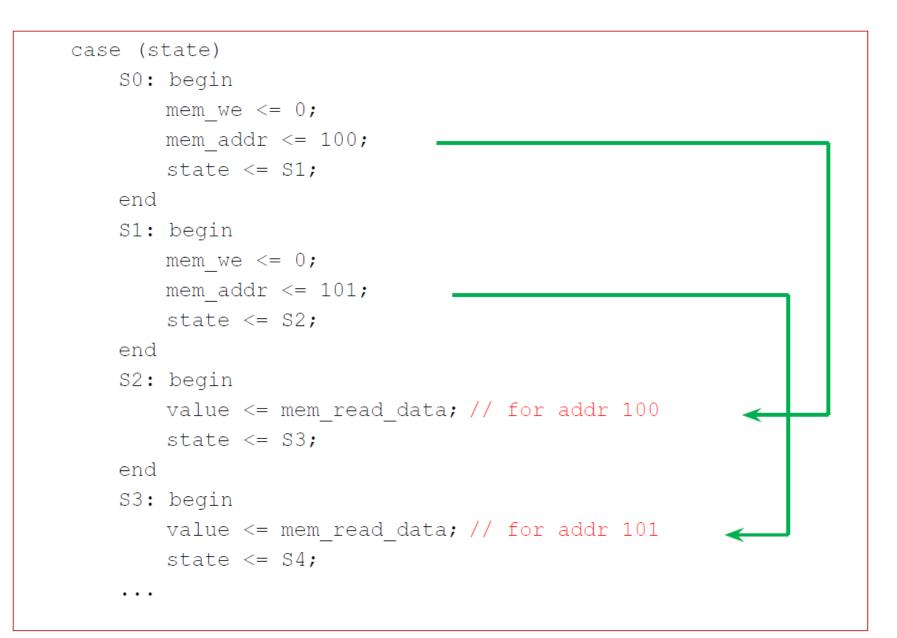

- Read 640 bits message from testbench memory in chunks of 32bits words (i.e. read 20 locations from memory by incrementing address offset)

- Move to Block creation FSM state

- In Block FSM state, Create two message blocks each of 512 bits

- First message block has first 16 words of input message stored in 'w' array

- Second message block has 4 words of input message, value 1, padding 0 and message size 640

- Assign h0, h1, h2, h3, h4, h5, h6, h7 to a, b, c, d, e, f, g, h respectively

- Check if for both blocks SHA256 operation has been processed and hash is created, if yes then move to WRITE state otherwise move to compute state

- Perform Word expansion of 16 elements of input message block (512 bits) and create total 64 word array each having 32 bits

- Perform 64 rounds of SHA operation to generate hash values in 'a' thru 'h' array. Increment number of blocks iteration variable

- Add previous hash values with 'a' thru 'h' hash values, go back to BLOCK State

- Write 256 bit hash value stored in h0 to h7 hash variables in testbench memory using output\_addr as a starting address location

- Set done = 1 and then move to IDLE state

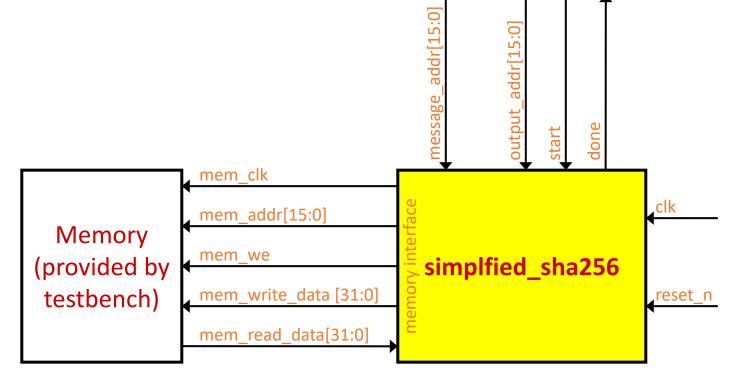

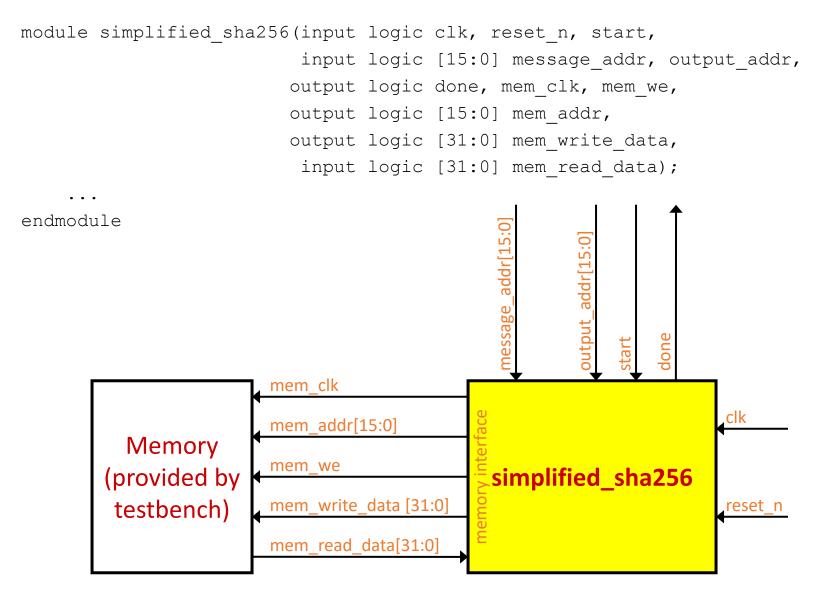

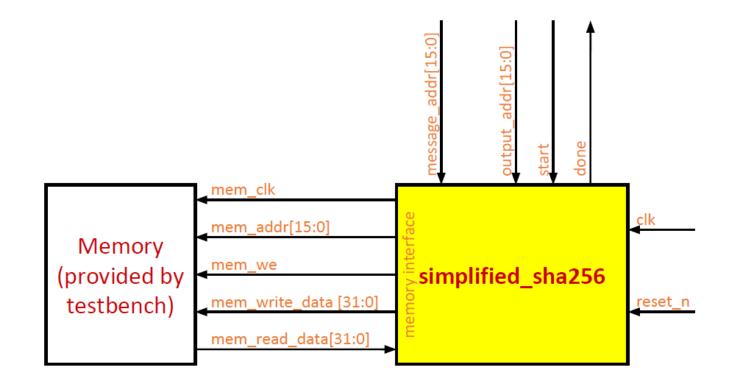

## **Module Interface**

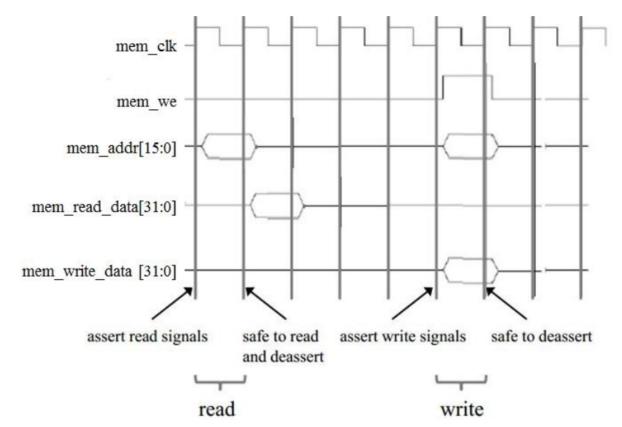

- Wait in idle state for start, read message starting at message\_addr and write final hash {H0, H1, H2, H3, H4, H5, H6, H7} in 8 words to memory starting at output\_addr. message\_addr and output\_addr are word addresses.

- □ Message size is "hardcoded" to 20 words (640 bits).

- □ Set **done** to 1 when finished.

- Testbench has memory defined named "dpsram[0:16383]" which has all 20 word of input message available

#### **Module Interface**

Write the final hash {H0, H1, H2, H3, H4, H5, H6, H7} in 8 words to memory starting at output\_addr as follows:

```

mem_addr <= output_addr;

mem_write_data <= H<sub>0</sub>; output_addr |

mem_addr <= output_addr + 1; output_addr + 1

mem_write_data <= H<sub>1</sub>; output_addr + 2

... output_addr + 3

mem_addr <= output_addr + 7; output_addr + 4

mem_write_data <= H<sub>7</sub>; output_addr + 5

```

output\_addr + 5 output\_addr + 6

output\_addr + 7

| addr  | HO |

|-------|----|

| r + 1 | H1 |

| r + 2 | H2 |

| r + 3 | H3 |

| r + 4 | H4 |

| r + 5 | H5 |

| r + 6 | H6 |

| r + 7 | H7 |

#### **Module Interface**

#### □ Your assignment is to design the yellow box:

## **No Inferred Megafunctions or Latches**

#### □ In your Quartus compilation message ensure :

- No inferred megafunctions: Most likely caused by block memories or shift-register replacement. Can turn OFF "Automatic RAM Replacement" and "Automatic Shift Register Replacement" in "Advanced Settings (Synthesis)". If you still see "inferred megafunctions", contact Professor. Your design will not pass if it has inferred megafunctions.

- No inferred latches: Your design will not pass if it has inferred latches.

## **No Block Memory Bits**

#### □ In your bitcoin\_hash.fit it <u>must</u> say **Total block memory bits is 0** (otherwise will not pass).

| ; | Fitter Summary            |   |                                             | ;  |

|---|---------------------------|---|---------------------------------------------|----|

| ; | Fitter Status             |   | Successful - Wed May 09 15:37:04 2018       | ;  |

| ; | Quartus Prime Version     | ; | 17.1.0 Build 590 10/25/2017 SJ Lite Edition | ;  |

| ; | Revision Name             | ; | bitcoin hash                                | ;  |

| ; | Top-level Entity Name     | ; | bitcoin hash                                |    |

| ; | Family                    | ; | Arria II GX                                 |    |

| ; | Device                    | ; | EP2AGX45DF29I5                              |    |

| ; | Timing Models             | ; | Final                                       | ;  |

| ; | Logic utilization         | ; | 8 %                                         | ;  |

| ; | Combinational ALUTS       | ; | 2,009 / 36,100 ( 6 % )                      | ;  |

| ; | Memory ALUTs              | ; | 0 / 18,050 ( 0 % )                          | ;  |

| ; | Dedicated logic registers | ; | 1,257 / 36,100 ( 3 % )                      | ;  |

| ; | Total registers           | ; | 1257                                        | ;  |

| ; | Total pins                | ; | 118 / 404 ( 29 % )                          | ;  |

| ; | Total virtual pins        | ; | 0                                           | ;  |

| ; | Total block memory bits   | ; | 0 / 2,939,904 ( 0 % )                       | -, |

| ; | DSP block 18-bit elements | ; | 0 / 232 ( 0 % )                             | ;  |

□ If not, go to "Assignments→Settings" in Quartus, go to "Compiler Settings", click "Advanced Settings (Synthesis)"

Turn OFF "Auto RAM Replacement" and "Auto Shift Register Replacement"

#### 🖌 Advanced Analysis & Synthesis Settings

Specify the settings for the logic options in your project. Assignments made to an individual node or entity in the Assignment Editor will override the option settings in this dialog box.

| altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals,<br>must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Analysis & Synthesis Message Level       Medium         Auto Carry Chains       On         Auto Clock Enable Replacement       On         Auto DSP Block Replacement       On         Auto Gated Clock Conversion       Off         Auto Open-Drain Pins       On         Auto RAM Block Balancing       On         Auto RAM Block Balancing       On         Auto RAM Replacement       Off         Auto RAM Replacement       Off         Auto RAM Replacement       Off         Auto RAM Replacement       Off         Auto ROM Replacement       Off         Auto Roll Conversion       Off         Auto Roll Conversion       Off         Auto RAM to Logic Cell Conversion       Off         Auto ROM Replacement       On         Auto Roll Replacement       Off         Auto Roll Replacement       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Reset         Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must h                                                                                                                                                                                                                                                                                                                                                                                | Name:                                         | Setting:                                                 |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------|---------|

| Auto Carry Chains       On         Auto Clock Enable Replacement       On         Auto DSP Block Replacement       On         Auto Gated Clock Conversion       Off         Auto Open-Drain Pins       On         Auto RAM Block Balancing       On         Auto RAM Replacement       Off         Auto RAM Replacement       Off         Auto RAM Replacement       Off         Auto RAM Replacement       Off         Auto ROM Replacement       On         Auto ROM Replacement       Off         Auto ROM Replacement       Off         Auto ROM Replacement       Off         Auto ROM Replacement       Off         Auto ROM Replacement       On         Auto ROM Replacement       Off         Auto Rom Replacement       Off         Auto Rom Replacement       Off         Auto Rout Resource Sharing       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Itshift_taps megafunction. The shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have | Auto Carry Chains       On         Auto Clock Enable Replacement       On         Auto DSP Block Replacement       On         Auto Gated Clock Conversion       Off         Auto Open-Drain Pins       On         Auto RAM Block Balancing       On         Auto RAM Replacement       Off         Auto RAM Replacement       Off         Auto RAM Replacement       Off         Auto RAM Replacement       Off         Auto ROM Replacement       Off         Auto ROM Replacement       Off         Auto Robit Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three registers apart.       Reset Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                                                                                                                                                                                                                                                  | Allow Synchronous Control Signals             | On                                                       |         |

| Auto Clock Enable Replacement       On         Auto DSP Block Replacement       On         Auto Gated Clock Conversion       Off         Auto Open-Drain Pins       On         Auto RAM Block Balancing       On         Auto RAM Block Balancing       On         Auto RAM Replacement       Off         Auto RAM to Logic Cell Conversion       Off         Auto ROM Replacement       On         Auto RAM to Logic Cell Conversion       Off         Auto RAM to Logic Cell Conversion       Off         Auto Robin Replacement       On         Auto Robin Replacement       On         Auto Robin Replacement       Off         Auto Robin Replacement       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       To         Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                      | Auto Clock Enable Replacement       On         Auto DSP Block Replacement       On         Auto Gated Clock Conversion       Off         Auto Open-Drain Pins       On         Auto RAM Block Balancing       On         Auto RAM Block Balancing       On         Auto RAM Replacement       Off         Auto RAM to Logic Cell Conversion       Off         Auto ROM Replacement       On         Auto ROM Replacement       On         Auto Robin Register Replacement       Off         Auto Shift Register Replacement       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three registers apart.       Reset Allows the Compiler to find a group of shift registers for the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                                                                                                                                                                                                                                                                                                                    | Analysis & Synthesis Message Level            | Medium                                                   |         |

| Auto DSP Block Replacement       On         Auto Gated Clock Conversion       Off         Auto Open-Drain Pins       On         Auto RAM Block Balancing       On         Auto RAM Block Balancing       On         Auto RAM Replacement       Off         Auto RAM to Logic Cell Conversion       Off         Auto RAM to Logic Cell Conversion       Off         Auto RAM Replacement       On         Auto RAM Replacement       Off         Auto RAM to Logic Cell Conversion       Off         Auto RAM to Logic Cell Conversion       Off         Auto RAM Replacement       On         Auto Resource Sharing       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       To         Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                                                              | Auto DSP Block Replacement       On         Auto Gated Clock Conversion       Off         Auto Open-Drain Pins       On         Auto RAM Block Balancing       On         Auto RAM Block Balancing       On         Auto RAM Replacement       Off         Auto RAM to Logic Cell Conversion       Off         Auto RAM to Logic Cell Conversion       Off         Auto RAM Replacement       On         Auto RAM Replacement       Off         Auto RAM Replacement       Off         Auto Room Replacement       Off         Auto Resource Sharing       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Illows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three registers apart.       Reset Allows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Auto Carry Chains                             | On                                                       |         |

| Auto Gated Clock Conversion       Off         Auto Open-Drain Pins       On         Auto RAM Block Balancing       On         Auto RAM Block Balancing       On         Auto RAM Replacement       Off         Auto RAM to Logic Cell Conversion       Off         Auto ROM Replacement       On         Auto ROM Replacement       On         Auto Source Sharing       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                                                                                                                                                                                                                                                                                                                          | Auto Gated Clock Conversion       Off         Auto Open-Drain Pins       On         Auto RAM Block Balancing       On         Auto RAM Replacement       Off         Auto RAM to Logic Cell Conversion       Off         Auto ROM Replacement       On         Auto ROM Replacement       On         Auto ROM Replacement       On         Auto ROM Replacement       On         Auto ROM Replacement       Off         Auto Resource Sharing       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three registers apart.       Reset Allows the Compiler to find a group of signals, and must have equally spaced taps that are at least three registers apart.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Auto Clock Enable Replacement                 | On                                                       |         |

| Auto Open-Drain Pins       On         Auto RAM Block Balancing       On         Auto RAM Block Balancing       On         Auto RAM Replacement       Off         Auto RAM to Logic Cell Conversion       Off         Auto ROM Replacement       On         Auto ROM Replacement       On         Auto Source Sharing       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                                                                                                                                                                                                                                                                                                                                                                        | Auto Open-Drain Pins       On         Auto RAM Block Balancing       On         Auto RAM Replacement       Off         Auto RAM to Logic Cell Conversion       Off         Auto ROM Replacement       On         Auto ROM Replacement       On         Auto ROM Replacement       On         Auto ROM Replacement       Off         Auto Robit Register Replacement       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Illows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three registers apart.       Reset Altors approximation ap | Auto DSP Block Replacement                    | On                                                       |         |

| Auto RAM Block Balancing       On         Auto RAM Replacement       Off         Auto RAM to Logic Cell Conversion       Off         Auto ROM Replacement       On         Auto Room Replacement       On         Auto Shift Register Replacement       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Auto RAM Block Balancing       On         Auto RAM Replacement       Off         Auto RAM to Logic Cell Conversion       Off         Auto ROM Replacement       On         Auto Rom Replacement       On         Auto Rom Replacement       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three registers apart.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Auto Gated Clock Conversion                   | Off                                                      |         |

| Auto RAM Replacement       Off         Auto RAM to Logic Cell Conversion       Off         Auto ROM Replacement       On         Auto Rom Replacement       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Image: Convert Conversion of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Auto RAM Replacement       Off         Auto RAM to Logic Cell Conversion       Off         Auto ROM Replacement       On         Auto Resource Sharing       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three registers apart.       Reset Allows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Auto Open-Drain Pins                          | On                                                       |         |

| Auto RAM to Logic Cell Conversion       Off         Auto ROM Replacement       On         Auto Resource Sharing       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Auto RAM to Logic Cell Conversion       Off         Auto ROM Replacement       On         Auto Resource Sharing       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three registers apart.       Reset Allows the compiler to find a group of signals, and must have equally spaced taps that are at least three registers apart.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Auto RAM Block Balancing                      | On                                                       |         |

| Auto ROM Replacement       On         Auto Resource Sharing       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Auto ROM Replacement       On         Auto Resource Sharing       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three registers apart.       Reset Allows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Auto RAM Replacement                          | Off                                                      |         |

| Auto Resource Sharing       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Auto Resource Sharing       Off         Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three registers apart.       Reset Allows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Auto RAM to Logic Cell Conversion             | Off                                                      |         |

| Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Auto Shift Register Replacement       Off         Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three registers apart.       Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Auto ROM Replacement                          | On                                                       |         |

| Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Block Design Naming       Auto         Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three registers apart.       Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Auto Resource Sharing                         | Off                                                      |         |

| Carry Chain Length 70 Description: Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Carry Chain Length       70         Description:       Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three registers apart.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Auto Shift Register Replacement               | Off                                                      |         |

| Description:<br>Allows the Compiler to find a group of shift registers of the same length that can be replaced with the<br>altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals,<br>must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Description:<br>Allows the Compiler to find a group of shift registers of the same length that can be replaced with the<br>altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals,<br>must not have any other secondary signals, and must have equally spaced taps that are at least three<br>registers apart.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Block Design Naming                           | Auto                                                     |         |

| Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Allows the Compiler to find a group of shift registers of the same length that can be replaced with the altshift_taps megafunction. The shift registers must all use the same clock and clock enable signals, must not have any other secondary signals, and must have equally spaced taps that are at least three registers apart.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Carry Chain Length                            | 70                                                       |         |

| altshift_taps megafunction. The shift registers must all use the same clock and clock enable sig<br>must not have any other secondary signals, and must have equally spaced taps that are at least                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | altshift_taps megafunction. The shift registers must all use the same clock and clock enable sig<br>must not have any other secondary signals, and must have equally spaced taps that are at least<br>registers apart.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Carry Chain Length                            |                                                          |         |

| registers apart.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | altshift_taps megafunction. The shift registe | rs must all use the same clock and clock enable signals, |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | registers apart.                              |                                                          | Reset A |

## **Final Project Submission**

#### **D** Put following files into (LastName, FirstName)\_(LastName, FirstName)\_finalproject.zip

- Both design files and also testbench code for both SHA256 and Bitcoin hashing project

- Modelsim transcript files msim\_transcript for both SHA256 and Bitcoin hashing project

- For both SHA256 and bitcoin hashing provide, fitter and sta files (files with extension .fit, .sta)

- Report for both SHA256 and Bitcoin hashing project

- Finalsummary.xls file with fmax, number of cycles, aluts, registers detail filled. Template of this file is

provided as part of Final\_Project.zip folder. This should be submitted for both SHA256 and bitcoin hash

#### □ Final report should including following mentioned :

- Explain briefly what SHA-256 is and bitcoin hashing (may use lecture slide contents)

- Describe algorithm for both SHA-256 and Bitcoin hashing implemented in your code

- Simulation waveform snapshot for both SHA-256 and Bitcoin hashing

- Provide modelsim transcript window output indicating passing test results generated from self-checker in testbench for both SHA-256 and Bitcoin hashing

- Provide synthesis resource usage and timing report for bitcoin\_hash only.

- Should include ALUTs, Registers, Area, Fmax snapshots

- Provide fitter report snapshot

- Provide Timing Fmax report snapshots

- Make sure to use Arria II GX EP2AGX45DF29I5 device and use Fmax for Slow 900mV 100C Mod

# Fill up finalsummary.xlsx

□ Fill up finalsummary.xlsx posted on Piazza as part of Final\_Project.zip (to be filled for both simplified\_sha256 bitcoin\_hash project in separate fillsummary.xlsx)

|           |                 |            |           |                  |                   |        |            |       | Fmax   |         | Delay      | Area*Delay      |

|-----------|-----------------|------------|-----------|------------------|-------------------|--------|------------|-------|--------|---------|------------|-----------------|

| Last Name | First Name      | Student ID | SectionId | Email            | Compiler Settings | #ALUTs | #Registers | Area  | (MHz)  | #Cycles | (microsec) | (millisec*area) |

| SMITH     | ROBERT BENJAMIN | A12345678  | 925042    | r.smith@ucsd.edu | balanced          | 31607  | 20932      | 52539 | 134.01 | 242     | 1.806      | 94.877          |

| JONES     | ALICE MARIE     | A23456789  | 925044    | a.jones@ucsd.edu | balanced          | 31607  | 20932      | 52539 | 134.01 | 242     | 1.806      | 94.877          |

|           | 1               |            |           |                  |                   |        | 1          |       |        |         |            |                 |

□ If you worked alone, just fill out one row

- □ Spreadsheet already contains calculation fields: e.g. Area = #ALUTs + #Registers. Please use them.

- Students to fill ALUTs, Registers, Fmax and Cycles column in excel sheet.

- □ #cycles will be generated for your design from testbench code.

- □ Make sure to use Arria II GX EP2AGX45DF29I5 device

- □ Make sure to use Fmax for Slow 900mV 100C Model

- □ Make sure to use **Total number of cycles**

Note : Best Fmax with area will be considered as one of the grading point for bitcoin hashing project.

## simplified\_sha256.fit & bitcoin\_hash.fit Fitter Report

Copy of the <u>fitter reports (not the flow report</u>) with area numbers.

□ Make sure to use Arria II GX EP2AGX45DF29I5 device

□ IMPORTANT: Make sure Total block memory bits is 0.

|                                   | -+                                            |

|-----------------------------------|-----------------------------------------------|

| Fitter Status                     | ; Successful - Wed May 09 15:37:04 2018       |

| Quartus Prime Version             | ; 17.1.0 Build 590 10/25/2017 SJ Lite Edition |

| Revision Name                     | ; bitcoin_hash                                |

| Top-level Entity Name             | ; bitcoin_hash                                |

| Family                            | ; Arria II GX                                 |

| Device                            | ; EP2AGX45DF29I5                              |

| Timing Models                     | ; Final                                       |

| Logic utilization                 | ; 8 %                                         |

| Combinational ALUTs               | ; 2,009 / 36,100 ( 6 % )                      |

| Memory ALUTs                      | ; 0 / 18,050 ( 0 % )                          |