# CPEN400P: Intermediate Representations

Lecture 2

Karthik Pattabiraman, UBC

Most of the material in this lecture comes from Chapter 5 of EaC

Copyright 2010, Keith D. Cooper & Linda Torczon, all rights reserved.

Students enrolled in Comp 412 at Rice University have explicit permission to make copies of these materials for their personal use.

Faculty from other educational institutions may use these materials for nonprofit educational purposes, provided this copyright notice is preserved.

# Learning Objectives

- List the desirable features of intermediate representations

- List the types of Intermediate Representations and their types of abstractions

- Understand the pros and cons of different intermediate representations

- Understand SSA form and it's advantages

- List the pros and cons of various memory models

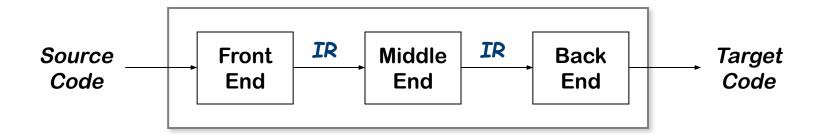

## Intermediate Representations: 3-pass compiler

- Front end produces an intermediate representation (IR)

- Middle end transforms the IR into an equivalent IR that runs more efficiently

- Back end transforms the IR into native code

- IR encodes the compiler's knowledge of the program

- Middle end usually consists of several passes

## Intermediate Representations

- Decisions in IR design affect the speed and efficiency of the compiler

- Some important IR properties

- Ease of generation

- Ease of manipulation

- Procedure size

- Freedom of expression

- Level of abstraction

- The importance of different properties varies between compilers

- Selecting an appropriate IR for a compiler is critical

# Types of Intermediate Representations

#### Three major categories

- Structural

- Graphically oriented

- Heavily used in source-to-source translators

- Tend to be large

Examples: Trees, DAGs

- Linear

- Pseudo-code for an abstract machine

- Level of abstraction varies

- Simple, compact data structures

- Easier to rearrange

- Hybrid

- Combination of graphs and linear code

- Example: control-flow graph

Examples:

3 address code

Stack machine code

Example: Control-flow graph, SSA form

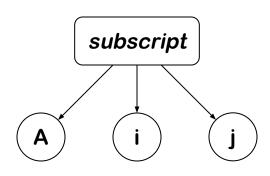

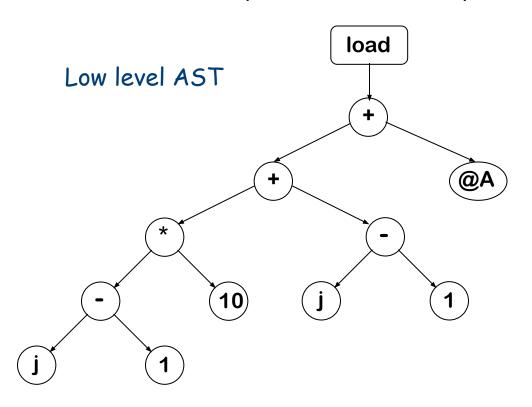

#### Level of Abstraction

- The level of detail exposed in an IR influences the profitability and feasibility of different optimizations.

- Two different representations of an array reference:

High level AST: Good for memory disambiguation

loadI 1 =>

$$r_1$$

sub  $r_1$ ,  $r_1$  =>  $r_2$

loadI 10 =>  $r_3$

mult  $r_2$ ,  $r_3$  =>  $r_4$

sub  $r_1$ ,  $r_1$  =>  $r_5$

add  $r_4$ ,  $r_5$  =>  $r_6$

loadI @A =>  $r_7$

add  $r_7$ ,  $r_6$  =>  $r_8$

load  $r_8$  =>  $r_{Aii}$

Low level linear code:

Good for address calculation

#### Level of Abstraction

- Structural IRs are usually considered high-level

- Linear IRs are usually considered low-level

- Not necessarily true see example below

loadArray A,i,j

High level linear code

# Learning Objectives

- List the desirable features of intermediate representations

- List the types of Intermediate Representations and their types of abstractions

- Understand the pros and cons of different intermediate representations

- Understand SSA form and it's advantages

- List the pros and cons of various memory models

# Abstract Syntax Tree

An abstract syntax tree is the procedure's parse tree with the nodes for most non-terminal nodes removed

- Can use linearized form of the tree

- Easier to manipulate than pointers

- x 2 y \* in postfix form

- \* 2 y  $\times$  in prefix form

- S-expressions (Scheme, Lisp) are (essentially) ASTs

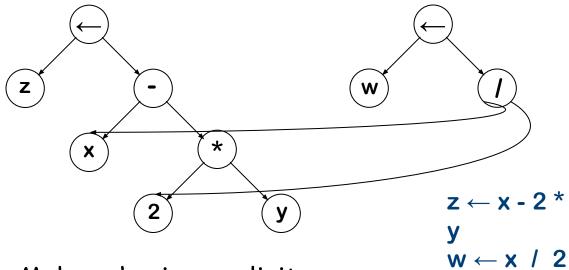

# Directed Acyclic Graph

A directed acyclic graph (DAG) is an AST with a unique node for each value

- Makes sharing explicit

- Encodes redundancy

With two copies of the same expression, the compiler might be able to arrange the code to evaluate it only once.

#### Stack Machine Code

#### Originally used for stack-based computers, now Java

Example:

push x

push 2

push y

multiply

subtract

#### Advantages

- Compact form

- Introduced names are implicit, not explicit

- Simple to generate and execute code

Useful where code is transmitted over slow communication links (the net)

Implicit names take up no space, where explicit ones do!

#### Three Address Code

#### Several different representations of three address code

In general, three address code has statements of the form:

$$x \leftarrow y \underline{op} z$$

With 1 operator  $(\underline{op})$  and, at most, 3 names (x, y, & z)

#### Example:

$$z \leftarrow x - 2 * ybecomes$$

$$t \leftarrow 2 * y$$

$$z \leftarrow x - t$$

#### Advantages:

- Resembles many real machines

- Introduces a new set of names \*

- Compact form

# Three Address Code: Quadruples

#### Naïve representation of three address code

- Table of k \* 4 small integers

- Simple record structure

- Easy to reorder

- Explicit names

load r1, y

loadI r2, 2

mult r3, r2, r1

load r4, x

sub r5, r4, r3

RISC assembly code

The original FORTRAN compiler used "quads"

| load  | 1 | У |   |

|-------|---|---|---|

| loadi | 2 | 2 |   |

| mult  | 3 | 2 | 1 |

| load  | 4 | х |   |

| sub   | 5 | 4 | 3 |

Quadruples

# Three Address Code: Triples

- Index used as implicit name

- 25% less space consumed than quads

- Much harder to reorder

| (1) | load  | У   |     |

|-----|-------|-----|-----|

| (2) | loadI | 2   |     |

| (3) | mult  | (1) | (2) |

| (4) | load  | х   |     |

| (5) | sub   | (4) | (3) |

Implicit names occupy no space

Remember, for a long time, 640Kb was a lot of RAM

#### Two Address Code

Allows statements of the form

$$x \leftarrow x op y$$

Has 1 operator  $(\underline{op})$  and, at most, 2 names (x and y)

#### Example:

$$z \leftarrow x - 2 * y$$

becomes

Can be very compact

$$t_{1} \leftarrow 2$$

$$t_{2} \leftarrow load y$$

$$t_{2} \leftarrow t_{2} * t_{1}$$

$z \leftarrow load x$

$z \leftarrow z - t_2$

#### Problems

- Machines no longer rely on destructive operations

- Difficult name space

- Destructive operations make reuse hard

- Good model for machines with destructive ops (PDP-11)

# Learning Objectives

- List the desirable features of intermediate representations

- List the types of Intermediate Representations and their types of abstractions

- Understand the pros and cons of different intermediate representations

- Understand SSA form and it's advantages

- List the pros and cons of various memory models

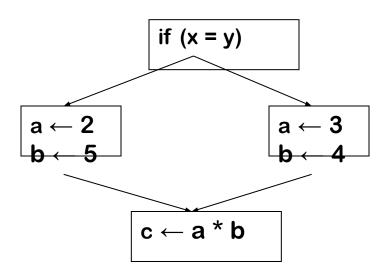

# Control-flow Graph

#### Models the transfer of control in the procedure

- Nodes in the graph are basic blocks

- Can be represented with quads or any other linear representation

- Edges in the graph represent control flow

### Example

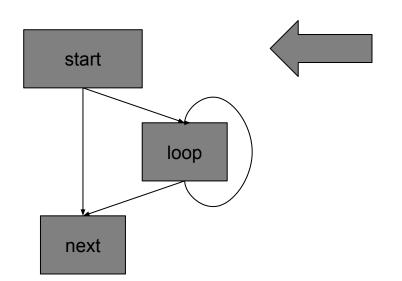

# Algorithm for converting linear code to CFG

- Find leaders

- Identify all nodes that are labels/targets for jumps as leaders

- Break CFG into (leader, last) pairs

- For each leader, traverse program until we come to another leader. Terminate the block and record (leader, last) pair.

- If the last instruction is a conditional branch to 11, 12, then record edges from the current block to blocks 11 and 12

- If the last instruction is a unconditional branch to label 'l', then add an edge from the current block to 'l'

- If the last instruction is an indirect jump (e.g., jmp r1), then

- $\rightarrow$  Strategy 1 (conservative): Add an edge to every basic block

- → Strategy 2 (precise): Add an edge to only those basic blocks that

are targets of the jump requires pointer/alias analysis to resolve

Add an entry node and exit node and the corresponding arcs if needed

# Example of CFG Algorithm

#### **Original**

#### **BBs With explicit branches**

start:  $x \leftarrow ...$   $y \leftarrow ...$ if (x>k) goto next

loop:

$$x \leftarrow x + 1$$

$y \leftarrow y + x$

if  $(x < k)$  goto loop

next: ..

## Class Activity

Draw the CFG for the following code applying the algorithm in the previous slide for CFG construction (Figure 5.14 in EaC).

```

■ FIGURE 5.13 Code Fragment for Exercise 4.

L01: add

LO5: add

ra, rb

add

add

add

\Rightarrow r<sub>3</sub>

add

rc, rd

add

ra, rb

\Rightarrow r<sub>4</sub>

12i

cmp_LT r<sub>1</sub>,r<sub>2</sub>

add

r13, rb

\rightarrow L02,L04

multI

r<sub>12</sub>,17

LO2: add

ra, rb

jumpI

\rightarrow L03

multI

r6.17

\Rightarrow r<sub>7</sub>

L06: add

r1, r2

\Rightarrow r<sub>16</sub>

jumpI

\rightarrow L03

12i

\Rightarrow r<sub>17</sub>

L03: add

\Rightarrow r<sub>22</sub>

i2i

\Rightarrow r<sub>18</sub>

multI

r_{22},17 \Rightarrow r_{23}

add

r17, r18 => r19

jumpI

→ L07

add

r_{18}, r_{17} \Rightarrow r_{20}

LO4: add

rc, rd

multI

r1,17

⇒ r21

121

jumpI

→ L03

cmp_LT r_9, r_d \Rightarrow r_{10}

LO7: nop

cbr

r_{10} \rightarrow L_{05}, L_{06}

```

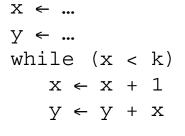

## Static Single Assignment (SSA) Form

- The main idea: each name defined exactly once

- Introduce  $\varphi$ -functions to make it work

Original

SSA-form

next:

```

x \leftarrow \dots

y \leftarrow \dots

while (x < k)

x \leftarrow x + 1

y \leftarrow y + x

```

```

x_0 \leftarrow \dots

y_0 \leftarrow \dots

if (x_0 >= k) \text{ goto next}

loop: x_1 \leftarrow \phi(x_0, x_2)

y_1 \leftarrow \phi(y_0, y_2)

x_2 \leftarrow x_1 + 1

y_2 \leftarrow y_1 + x_2

if (x_2 < k) \text{ goto loop}

```

#### Strengths of SSA-form

- Sharper analysis

- φ-functions give hints about placement

- Some facts are obvious (e.g., live variables)

- Compact representation of data-flow facts

# Algorithm to convert code to SSA (Naïve algorithm)

#### Non-obvious construction algorithm

- Will examine this algorithm later in this course

- Naïve algorithm inserts too many redundant phi functions

#### Naïve algorithm

- Traverse the code in linear order

- The first time you come to a variable, no action is needed

- When you come to a previously defined variable, rename it to a unique name and replace all references with the new name

- If you come to a Y-point in the code (i.e., control flow convergence), insert a phi node for every variable defined and used in the downstream computations, and add the predecessor block's latest values as operands of the phi instruction

- Not as simple as it looks

# Class Activity

Draw the CFG of the following code and convert it to SSA form (Example based on Figure 5.13 in EaC)

```

X ← ...

y ← ..

a \leftarrow y + 2

b \leftarrow 0

while (x < a) {

if (y < x) {

x \leftarrow y + 1

y ← b * 2

} else {

x \leftarrow y + 2

y \leftarrow a + 2;

w \leftarrow x + 2

z \leftarrow y * a

y \leftarrow y + 1

```

B2: if

$$(y \ge x)$$

jump B4

B3:

$$x \leftarrow y + 1$$

$y \leftarrow b * 2$

jump B5

B4:

$$x \leftarrow y + 2$$

$y \leftarrow a + 1$

B5: if

$$(x \ge a)$$

jump B2

B6:

$$w \leftarrow x + 2$$

$z \leftarrow y * a$

$y \leftarrow y + 1$

## Learning Objectives

- List the desirable features of intermediate representations

- List the types of Intermediate Representations and their types of abstractions

- Understand the pros and cons of different intermediate representations

- Understand SSA form and it's advantages

- List the pros and cons of various memory models

## Memory Models

#### Two major models

- Register-to-register model

- Keep all values that can legally be stored in a register in registers

- Ignore machine limitations on number of registers

- Compiler back-end must insert loads and stores

- Memory-to-memory model

- Keep all values in memory

- Only promote values to registers directly before they are used

- Compiler back-end can remove loads and stores

# Pros of Register-to-Register memory Model

- Compilers for RISC machines usually use register-to-register

- Reflects programming model

- Easier to determine when registers are used

- Does not limit number of registers in the target

- Easy to represent data-flow facts about the program (i.e., a value that is safe to move to a register is one that is not indirectly modified, through a pointer, for example)

# Cons of Register-to-Register Memory Model

- Pressure on downstream passes and register allocator

- Additional loads/stores required

- Can provide misleading information about program's performance at the intermediate code level

- Cannot reason about memory pressure, cache misses etc.

- Not a good match for register-constrained machines

- Handling memory references may be cumbersome at the IR level as the default mode is to operate on registers

- Need to ensure that any variable whose address can be taken cannot have multiple references to it (i.e., alias analysis)

- Such variables cannot be stored in registers

# Learning Objectives

- List the desirable features of intermediate representations

- List the types of Intermediate Representations and their types of abstractions

- Understand the pros and cons of different intermediate representations

- List the pros and cons of various memory models

#### TODOs in the near term

Find a partner to do the assignments with and send us a private note on Piazza by Jan 20th

Try tutorial 1 - installation and writing a simple pass in LLVM

- Needed for doing assignment 1 (Jan 21st release)

- You can get help from TAs during the lab session

Prepare for the PPT on Thursday (Jan 20th)

- Simple C++ programming problems

- Done online in the HR platform

Decide if you want to stay in the course or drop it (Jan 21)